改進的解耦雙同步坐標系鎖相環的設計與實現

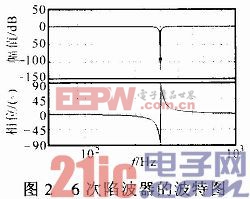

2.2 6次陷波器的設計

模擬陷波器的傳遞函數為:

由文獻可知,當諧振頻率為300 Hz,諧振點3 dB帶寬為30 Hz,可得到對應的數字陷波器的傳遞函數為:

陷波器的波特圖如圖2所示。由圖可見,該陷波器能夠很好地濾除300 Hz的諧波。本文引用地址:http://www.104case.com/article/175888.htm

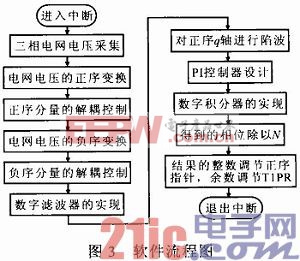

3 PLL的實現

電網電壓通過LV28-P芯片進行檢測,通過調理電路和電平抬升電路后將采樣得到的電網電壓轉換到0~3.3V范圍內.然后送入DSP2407。

dc相關文章:dc是什么

低通濾波器相關文章:低通濾波器原理

鎖相環相關文章:鎖相環原理 鎖相放大器相關文章:鎖相放大器原理

評論