基于微處理器的數字信號傳輸性能分析儀的研究

摘要:根據數字基帶傳輸系統的基本原理,設計了一套基于微處理的簡易數字信號傳輸性能分析儀,系統主要由數字信號發送模塊、信號傳輸模塊和數字信號接收分析模塊三部分構成,其中信號發送模塊由數字信號發生器和信道模擬低通濾波器等組成。整個系統采用微處理器STM32F103實現碼元速率的控制、信道切換、噪聲電平調節、擴頻與解擴以及同步信號的提取。系統經測試,解碼的曼徹斯特編碼數據與發送端完全一致,同步信號穩定和可靠。

關鍵詞:傳輸性能分析儀;微處理器;曼徹斯特編碼;眼圖

0 引言

隨著數字傳輸技術的廣泛應用,需要更多各種各樣的通信測試儀器完成系統參數的測量與調試。數字傳輸性能分析儀作為一種數字通信系統設計與檢測的設備在數字傳輸系統的工程施工與日常維護中發揮著重要的作用。本論文設計的是采用STM32F103實現的簡易數字信號傳輸性能分析儀,其傳輸數據速率為10~100kb/s范圍,并以10kb/s步進可調,設計的截止頻率為100kHz、200kHz與500kHz三個可選低通濾波器,其帶外衰減大于40dB/10倍頻程,通帶增益在0.2~4.0范圍內可調;并且設計了一個數據率為10Mb/s的m序列作為信道的加性噪聲,其輸出峰峰值為100mV~TTL電平可調。

1 系統方案實現

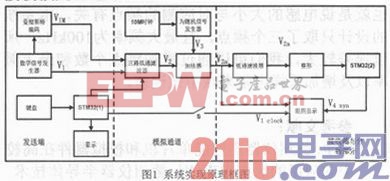

根據設計要求,構建了圖1所示的系統方框圖,整個系統主要包括信號發送部分和信號接收部分。發送部分主要包括基于STM32F103的ARM最小系統板及其構成的人機交互界面,m碼高速偽隨機信號發生器,m碼數字信號發生器及曼徹斯特編碼電路,截止頻率為100kHz、200k Hz、500kHz的3種通帶增益可調的低通模擬濾波器;接收部分主要包括信號接收預處理電路和基于ARM平臺的信號處理平臺。

2 軟硬件實現

2.1 信源電路

本系統所使用的信源為m序列與曼徹斯特碼兩種,其中m序列V1的生成多項式為f1(X)=1+x2+x3+x4+x8,將其輸出與時鐘相異或可得曼徹斯特碼輸出。為了可控輸出信號的碼型,如圖2所示的雙輸入端異或門的輸入clk(clk為m序列發生器的時鐘)端添加了一個雙輸入的與門,當CNT=1時,控制異或門輸出m序列的曼徹斯特碼編碼;當CNT=0時,控制異或門輸出系統所需的m序列。系統測試信道傳輸特性時所需的信號曲它們提供。

評論