一種低電壓低靜態電流LDO的電路設計(二)

2 電路設計與實現

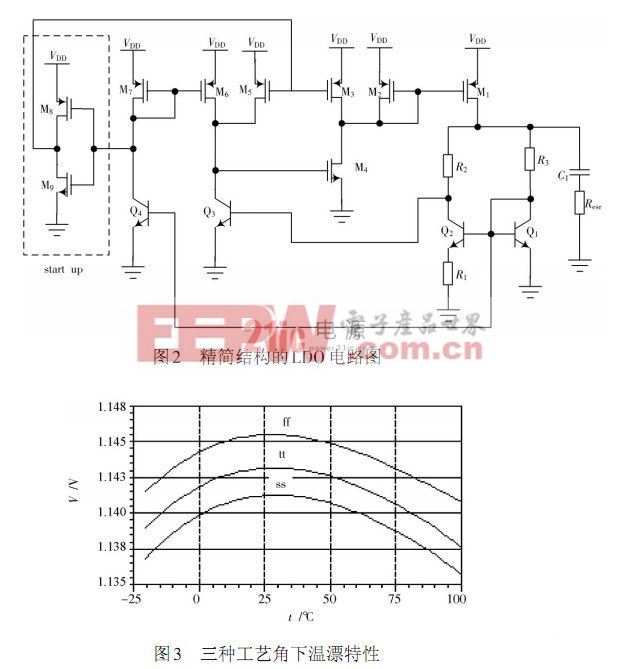

本文引用地址:http://www.104case.com/article/175289.htm本文所提的低電壓、低靜態電流的精簡結構的LDO如圖2所示。LDO的輸出級是一個A類共源級電路,包括PMOS功率管M1,三極管Q1、Q2,電阻R1,R2,R3,Resr和輸出負載補償電容C1.功率管M1有非常大的寬長比來驅動比較大的負載電流。因此M1的溝長選取最小的值,達到盡可能小的寄身電容和尺寸面積。為了獲取好的暫態輸出特性以及環路穩定,輸出補償電容取5 μF.帶隙基準電路包括三極管Q1,Q2,Q3和電阻R1,R2,R3.選取Q2的射級面積為Q1和Q3的射級面積8倍,這是Q2面積和R2阻值折中結果。三極管Q3和晶體管M6構成一個共集電極的電路,為環路提供高增益。緩沖級包括晶體管M2,M3和M4.因為NMOS源跟隨器,在低負載情況下并不能完全關斷功率管,PMOS源跟隨器并不適合本電路的1.35低電壓環境,所以選用了二極管連結的PMOS負載共源級電路作為緩沖級。這種結構不僅獲得低的輸出阻抗,同時達到180°的相位偏移,使整個閉環環路構成一個負反饋。M3作用是在低負載電流的情況是為M4提供一些偏置電流,否則可能出現M4的柵源電壓過低,導致三極管Q3進入飽和狀態,降低Q3的電流增益,影響帶隙基準電壓的精確度。通過Q4和M7構成的偏置電路,使得三極管Q1,Q3有相等的集電極電流。晶體管M5,M8和M9構成LDO的啟動電路。在剛有電壓輸入情況下,M8和M9構成一個反相器輸出一個低電壓信號,使M5導通來啟動整個電路。

3 電路仿真結果

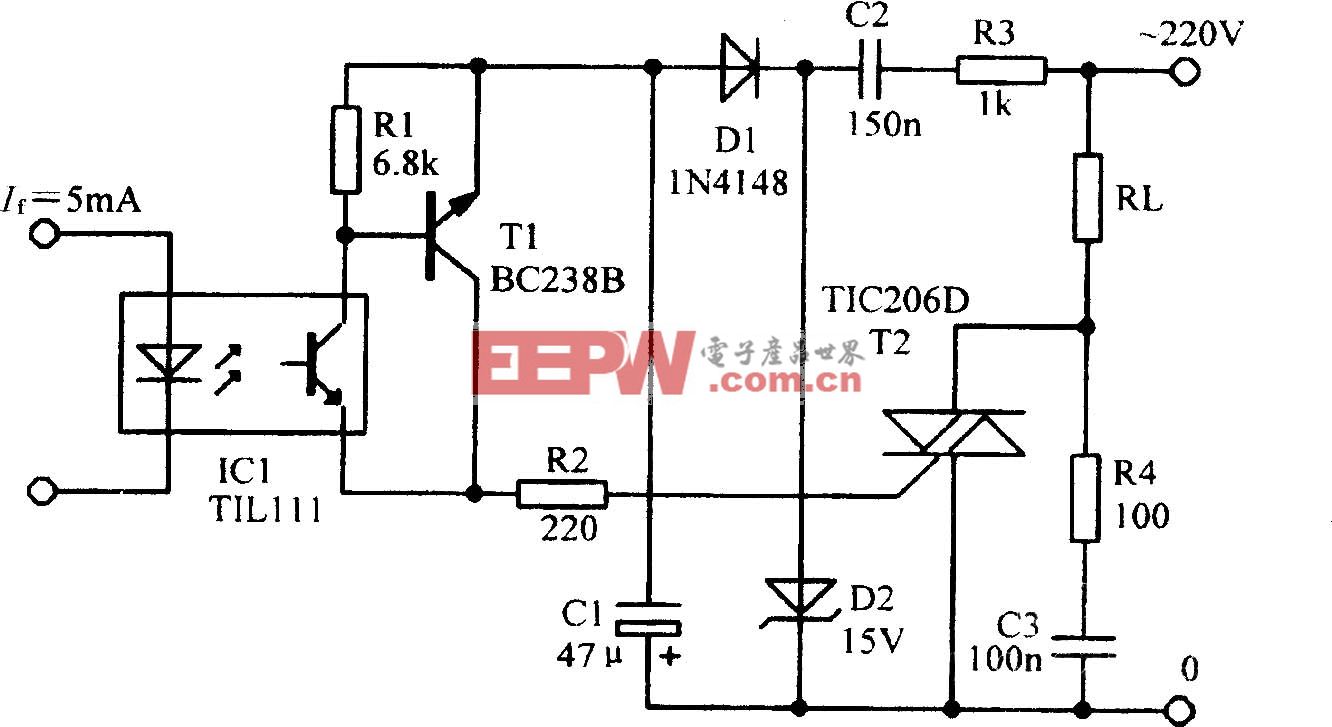

基于CSMC 0.5 μm 雙阱CMOS 工藝仿真模型,采用Cadence仿真軟件對精簡結構LDO進行了三個工藝角(tt,ff,ss)下仿真驗證。這個系統設計指標的是讓LDO驅動最大30 mA的負載電流,同時保持輸出電壓穩定在1.14 V,輸入電壓最小為1.35 V.LDO 的溫漂曲線如圖3所示。

通過采用補償電容外接串聯電阻的方法,創造一個左半平面的零點來補償一個非主極點,讓電路獲得比較好的環路相位裕度,在三個工藝角下,相位裕度都能達到70°(見圖4)。

評論