DSP中電源噪聲問題

具有較高時鐘率和速度的高速DSP系統設計正在變得日益復雜。結果,增加了噪聲源數。現在,高端DSP的時鐘率(1GHz)和速度(500MHZ)產生可觀的諧波,這些是由于PCB線跡的作用如同天線所致。由此引起的噪聲使音頻、視頻、圖像和通信功能降低并對達到FCC/CE商標認證造成問題。為了降低電源噪聲,對于高速DSP系統設計人員來講,識別和找出可能的噪聲原因以及采用良好的高速設計實踐是關鍵。本文說明交擾、鎖相環(PLL)、去耦/體電容器在降低噪聲中的重要性。

本文引用地址:http://www.104case.com/article/175264.htm降低交擾

交擾是一個重要的噪聲源。在高速系統中,信號地通路依賴于工作頻率。對于低速信號(10MHZ),電流經過最小電阻地通路(最短通路)返回到源。

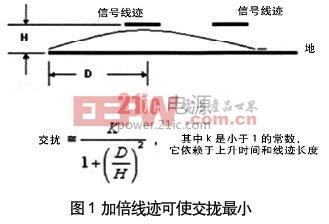

在10MHZ以上,情況就不同。經電流最小電感地通路返回。重要的是返回信號以電流分布傳播(圖1),這意味著相鄰信號的返回通路可能容易重疊,導致交擾。

降低交擾的技術有:線跡間距加大,增加地線,降低諧波分量和線跡端接技術。

在高速DSP系統中,加倍信號間的線跡間距,可降低環路重疊,使交擾降低4倍。對于差分信號(Earthnet或USB),建議間距所產生的信號對應具有所需的匹配阻抗。另外,關鍵信號(即時鐘)應屏蔽,路由信號在電源和地平板之間的內層,或把一個地平板放置在關鍵信號下面層上。

在再制板上加信號線時,應包括一個并聯地線。這可能提供高速電流返回通路并在電流環路中產生最小面積。這個附加的通路,確保返回電流不產生大的環路和拾取噪聲。

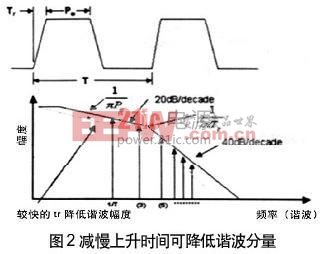

在降低交擾時,評價快速沿所引起的諧波和干擾是重要的。例如,在線跡上增加串聯終端電阻器,會使上升時間(Tr)減慢,這是有效地降低諧波分量的方法。噪聲幅度曲線在低頻能較好地衰減諧波分量(圖2)。

線跡可做為傳輸線(在上升時間Tr小于2倍傳播延遲時)。因此,應保持線跡盡可能的短。若線跡的長度足以做為傳輸線,則用串聯終端(電阻器與輸出驅動器串聯)或并聯終端(在負載處電阻器到地)接線。若電阻器與所用線跡PCB阻抗匹配,則可以降低傳輸線反射和瞬變。

鎖相環

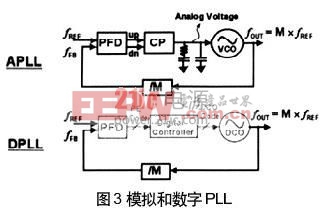

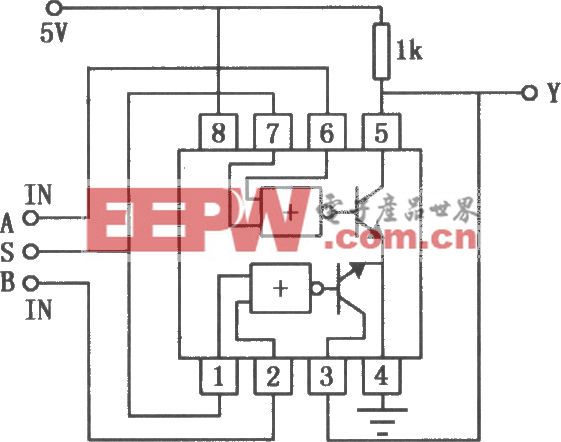

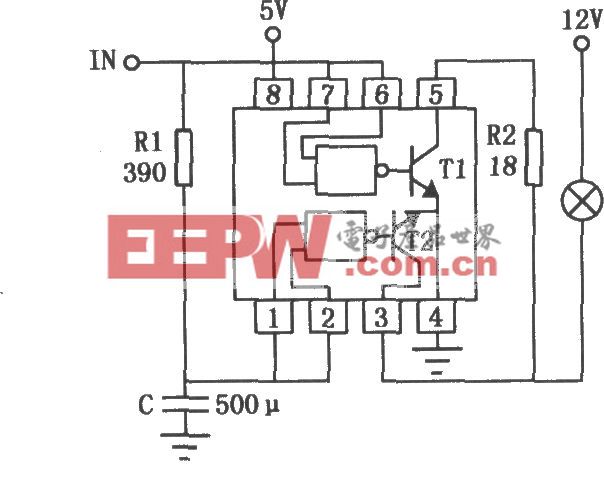

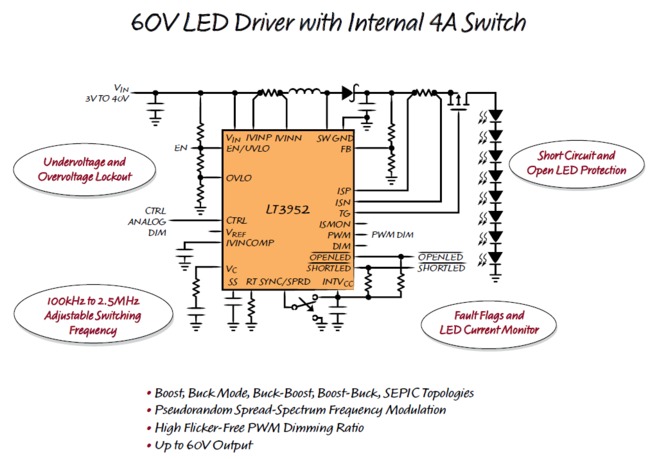

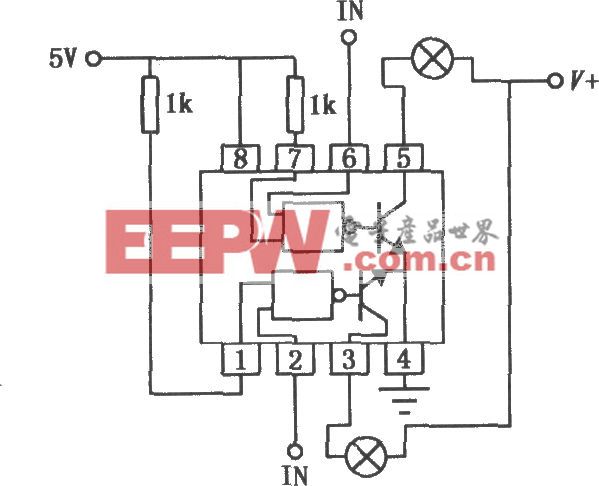

鎖相環(PLL)是另一個重要的噪聲源。在某些DSP中正日益采用模擬和數字版本PLL(圖3)。隔離到PLL電源時,用π形濾波器去除高頻噪聲是有效的。但它對去除低噪聲作用不大,需要用多級濾波器網絡。然而,在快速開關電路中,一個低壓降(LDO)穩壓器是更適合的,因為這種器件在低頻具有高電源抑制比(PSRR)。若設計的系統運行在噪聲環境(如汽車、電/機裝置),具有較大的低頻瞬變,則應選擇高PSRR穩壓器。

評論