基于FPGA的音樂硬件演奏電路設計與實現

3 系統的方案實現

本文引用地址:http://www.104case.com/article/175240.htm3.1 各模塊仿真及描述

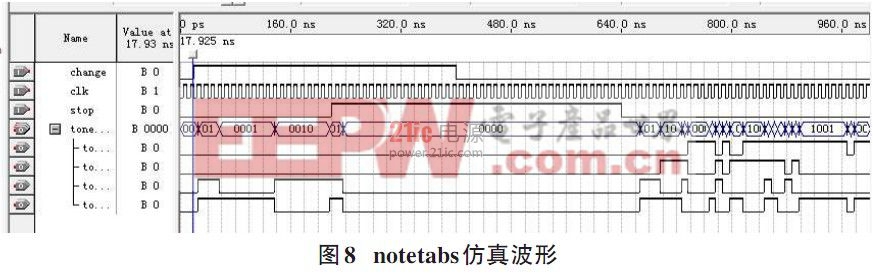

notetabs作為音符rom的地址發生器,此模塊中設置了一個8位2進制計數器,頻率為4hz,即為4個音符一秒時間四四拍的4分音符。notetabs計數器計數器按4hz時鐘頻率做加法計數,當stop為高電平時停止加法運算,而當change可設置rom中數據的跳轉,rom通過toneindex[30]端口輸向tonetaba模塊。樂曲就演奏起來了。

由圖6 sperkera仿真波形可以看出,當clk輸入時鐘頻率為12mhz時,輸出端信號clk輸出的頻率,隨tong信號的不同,輸出不同頻率的聲音信號。

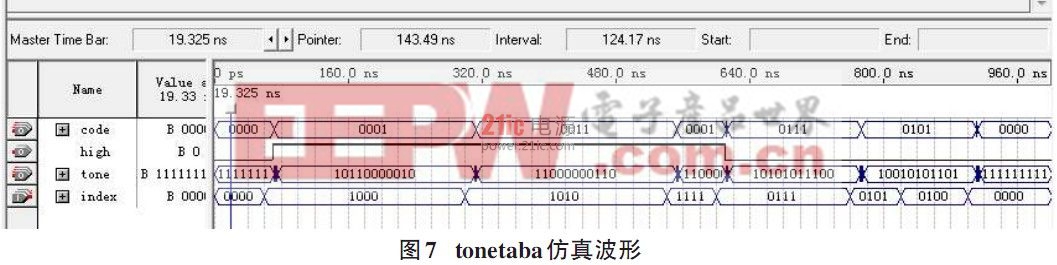

由圖7tonetaba信號的仿真波形,可以看出,當輸入信號index[30]輸入不同信號值,code輸出端輸出音符的顯示,high為音符高位信號,tone大于7時high為高電平。

圖8為notetabs仿真波形,當clk輸入時鐘信號,toneindex[30]端從rom中讀入音符數據,當輸入端口stop為“1”時,暫停從rom中讀入數據,stop為“0”繼續讀取音符信號,change為高低電平時,模塊分別讀取rom不同位置的數據。

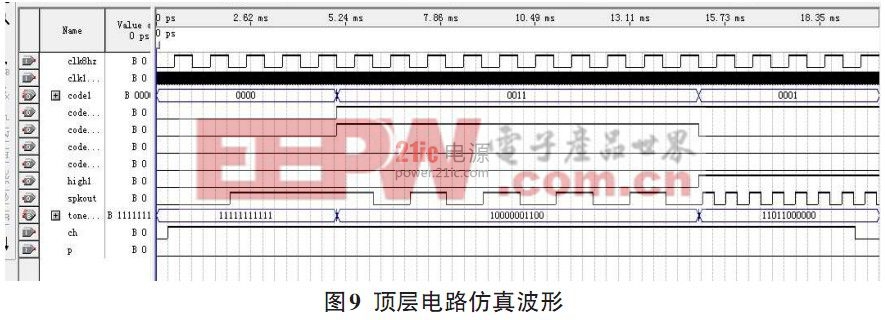

3.2 頂層電路仿真及描述

clk8hz端輸入8hz時鐘信號,另一個clk12mhz輸入12mhz時鐘信號,系統將自動從music.mif中讀取音符信號,以頻率不同輸出到spkout,同時輸出到顯示端口,和高音端口,code1[30],high1.p端口可以是音符暫停輸出(高電平時),ch端口控制歌曲間的切換。

4 硬件測試及說明

選擇實驗電路模式1,將引腳鎖定時clk12mhz于clock9連接,短路帽clock接12mhz.clk8hz與clock2連接。發音輸出spkout接speaker.簡譜碼輸出code1由數碼管5顯示,high高8度指示由發光管d5指示,p與按鍵d16連接,ch與的15連接。最后向目標芯片下載適配后的sof邏輯設計文件。

5 結論

本次設計在EDA開發工具QuartusII平臺上,應用語言層次化和模塊化的設計方法,通過音符編碼的設計思想,預先定制樂曲,在此基礎上設計了一個樂曲硬件演奏電路,經過對整體進行模塊化分析、編程、綜合、仿真及最終下載,完整實現簡易音樂器的播放功能。

通過學生自己手動完成簡單的數字器件的設計,在加強以傳統電子設計方法為基礎的工程設計訓練的同時,使學生能夠更快地掌握現代電子電路設計自動化的新方法和新手段,提高了學生對基礎實驗的興趣。

DIY機械鍵盤相關社區:機械鍵盤DIY

fpga相關文章:fpga是什么

手機電池相關文章:手機電池修復

塵埃粒子計數器相關文章:塵埃粒子計數器原理

評論