基于單片機(jī)和FPGA的頻率特性測(cè)試儀的設(shè)計(jì)

1 引言

頻率特性是網(wǎng)絡(luò)的性能最直觀反映。頻率特性測(cè)試儀是測(cè)量網(wǎng)絡(luò)的幅頻特性和相頻特性,并顯示相應(yīng)曲線的一種快速、方便、動(dòng)態(tài)、直觀的測(cè)量?jī)x器,可廣泛應(yīng)用于電子工程領(lǐng)域。

該測(cè)試儀以掃頻外差為基本原理,并以單片機(jī)和FPGA構(gòu)成的最小系統(tǒng)為控制核心,很好地完成對(duì)有源雙T網(wǎng)絡(luò)進(jìn)行頻率在100 Hz~100 kHz范圍內(nèi)的幅頻響應(yīng)和相頻響應(yīng)特性的測(cè)試,并實(shí)現(xiàn)在通用數(shù)字示波器上同時(shí)顯示幅頻和相頻響應(yīng)特性曲線。

2 系統(tǒng)設(shè)計(jì)方案

2.1 總體方案

該設(shè)計(jì)采用單片機(jī)和FPGA結(jié)合的方式。將輸出頻率可步進(jìn)的正弦信號(hào)的掃描信號(hào)源作為被測(cè)網(wǎng)絡(luò)的輸入信號(hào)Vi,則被測(cè)網(wǎng)絡(luò)的輸出信號(hào)Vo為頻率可步進(jìn)的信號(hào)。通過測(cè)量各頻率點(diǎn)的幅度就可得到Vo和Vi的有效值,兩者之比就是該點(diǎn)的幅度頻率響應(yīng);對(duì)Vo和Vi進(jìn)行過零比較、整形,再送到FPGA測(cè)量相位差。 Vi的上升沿啟動(dòng)計(jì)數(shù),Vo的上升沿停止計(jì)數(shù),所得時(shí)間值與信號(hào)周期之比,就是該點(diǎn)的相位頻率響應(yīng)。此方案采用FPGA測(cè)量相位差,而且便于制作DDS掃描信號(hào)源。

2.2 掃頻信號(hào)源設(shè)計(jì)方案

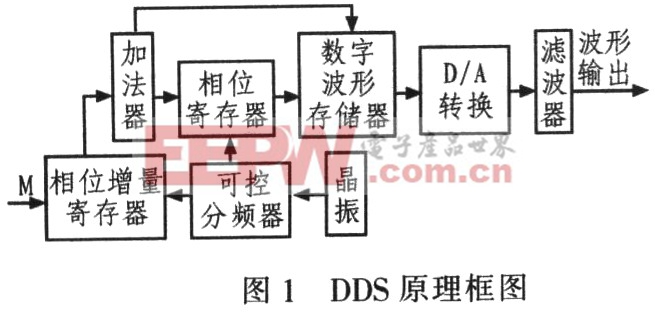

該設(shè)計(jì)采用直接數(shù)字合成(DDS)信號(hào)源。DDS信號(hào)源是由數(shù)字量控制的頻率源,如圖 1所示,其具體實(shí)現(xiàn)過程是:將輸出波形一個(gè)完整周期的幅度值按相位步進(jìn)順序量化存儲(chǔ)于雙端口RAM中,按一定的地址間隔讀出,經(jīng)D/A轉(zhuǎn)換成模擬信號(hào),再經(jīng)低通濾波器濾去D/A轉(zhuǎn)換帶來的小臺(tái)階和數(shù)字電路產(chǎn)生的毛刺,即可獲得高精度、高純度的正弦信號(hào)。理論上只要累加器的位數(shù)足夠多,便可實(shí)現(xiàn)任意小的頻率步進(jìn),且頻率分辨率很高,十分接近于連續(xù)變化。通過預(yù)設(shè)相位累加器初值可很方便地實(shí)現(xiàn)精密相位調(diào)節(jié)。

2.3 幅度測(cè)量模塊的方案

該模塊采用集成真有效值變換器件。測(cè)量被測(cè)信號(hào)的真有效值,然后將其換算為幅值。即可實(shí)現(xiàn)對(duì)正弦波的幅值測(cè)量。該方案硬件、軟件都很簡(jiǎn)單,而且精度高,效果理想。

評(píng)論