基于FPSLIC設(shè)計的DES解密和AES的分組加解密的實現(xiàn)

1 引言

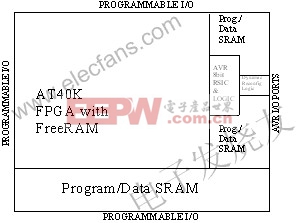

本文引用地址:http://www.104case.com/article/173220.htm美國Atmel公司生產(chǎn)的AT94K系列芯片是以Atmel0.35的5層金屬CMOS工藝制造。它基于SRAM的FPGA、高性能準(zhǔn)外設(shè)的Atmel8位RISCAVR單片機(jī)。另外器件中還包括擴(kuò)展數(shù)據(jù)和程序SRAM及器件控制和管理邏輯。圖1-1是Atmel公司的FPSLIC內(nèi)部結(jié)構(gòu)圖。

圖1-1FPSLIC內(nèi)部結(jié)構(gòu)圖

AT94K內(nèi)嵌AVR內(nèi)核,Atmel公司的FPSLIC可編程SOC內(nèi)嵌高性能和低功耗的8位AVR單片機(jī),最多還帶有36KB的SRAM,2個UART、1個雙線串行接口,3個定時/計數(shù)器、1個88乘法器以及一個實時時鐘。通過采用單周期指令,運算速度高達(dá)1MPS/MHz,這樣用戶可以充分優(yōu)化系統(tǒng)功耗和處理速度。AVR內(nèi)核基于增強(qiáng)型RISC結(jié)構(gòu),擁有豐富的指令系統(tǒng)以及32個通用工作寄存器。而且所有通用寄存器都與算術(shù)邏輯單元ALU相連;另外,在一個時鐘周期內(nèi),執(zhí)行單條指令時允許存取2個獨立的寄存器,這種結(jié)構(gòu)使得代碼效率更高,并且在相同的時鐘頻率下,可以獲得比傳統(tǒng)的CISC微處理器高10倍的數(shù)據(jù)吞吐量。AVR從片內(nèi)SRAM執(zhí)行程序,由于AVR運行代碼存儲在SRAM中,因此它可以提供比較大的吞吐量,這樣可以使其工作在突發(fā)模式上。在這種模式上,AVR大多時間都是處于低功耗待機(jī)狀態(tài),并能在很短的時間里進(jìn)行高性能的處理。微處理器在突發(fā)模式運行模式下的平均功耗要比長時間低頻率運行時的功耗低得多。FPSLIC的待機(jī)電流小于100,典型的工作電流為2-3mA/MHz。在系統(tǒng)上電時,F(xiàn)PGA配置SRAM和AVR程序SRAM都能自動地通過Atmel在系統(tǒng)可編程串行存貯器AT17來裝載。

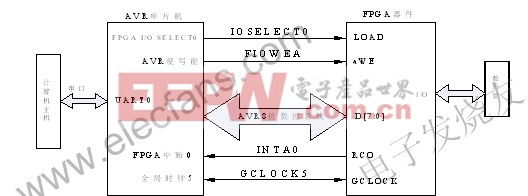

2.1 硬件實現(xiàn)框圖

圖2-1系統(tǒng)硬件實現(xiàn)框圖

圖2-1是為了實現(xiàn)加密算法的硬件框圖。計算機(jī)通過它的串口和FPSLIC的通信端口UART0相連,用來進(jìn)行數(shù)據(jù)的傳送和接收。FPSLIC通過AVR的通信端口等待接收主機(jī)傳來的信息,通過內(nèi)部的下載程序?qū)?shù)據(jù)進(jìn)行處理,最后再傳回到主機(jī)上。圖2-1中FPGA是一個計數(shù)器,此計數(shù)器一上電就從0計數(shù),并用進(jìn)位輸出信號產(chǎn)生一個AVR中斷,即進(jìn)位輸出信號RCO連接到AVR的中斷信號INTA0。當(dāng)AVR接收到由計數(shù)器的進(jìn)位信號產(chǎn)生的中斷時,則執(zhí)行INTA0的中斷服務(wù)程序(ISR)。在此期間,AVR就給INTA0產(chǎn)生的次數(shù)計數(shù),并把它放到8位的AVR-FPGA數(shù)據(jù)總線上,這時就會觸發(fā)AVR的寫使能信號(FPGA的aWE信號端)和FPGA的I/OSELECT0信號(FPGA的LOAD信號端),同時從AVR——FPGA數(shù)據(jù)總線上將數(shù)據(jù)載入計數(shù)器。數(shù)碼管的各極連接在實驗板上的可編程端口,通過引腳配置用來顯示數(shù)據(jù)。LED指示燈在AVRI/O輸出的D口,直接將數(shù)據(jù)通過命令PORTD來顯示。FPGA的時鐘通過GCLK5選自AVR單片機(jī)的時鐘。我們以DES數(shù)據(jù)加密為例,由仿真試驗可以得出DES加密的速率為57.024kbit/s,它大于串口的最大速率19.2kbit/s,因此可以實時進(jìn)行數(shù)據(jù)的加密操作。

一個典型的FPSLIC設(shè)計通常應(yīng)該包括以下幾個步驟:

1.利用聯(lián)合仿真軟件建立一個FPSLIC工程。

2.預(yù)先建立一個AVR軟件仿真程序文件。

3.預(yù)先建立一個FPGA的硬件仿真程序文件。

4.設(shè)置和運行AVR-FPGA接口設(shè)計。

5.運行布局前的聯(lián)合仿真Pre-layoutConverification(這一步是可選擇的)。

6.運行Figaro-IDS進(jìn)行FPGA的布局布線。

7.運行布局后的聯(lián)合仿真Pos-layoutConverification(這一步是可選擇的)。

8.器件編程數(shù)據(jù)下載與實驗驗證。

我們以DES數(shù)據(jù)加密為例,(新建的工程名為lab1.apj,AVR仿真程序文件為desjiami.asm,F(xiàn)PGA的硬件仿真程序為Count.vhdl)。

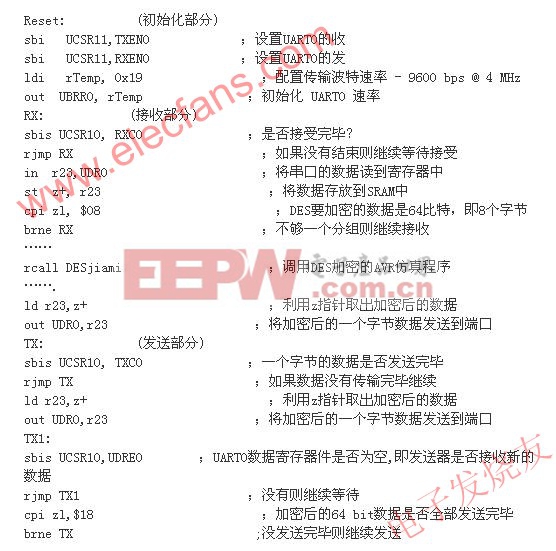

2.2 編譯AVR的仿真程序軟件

(以上程序代碼是整個仿真的程序框架,最主要的是對接口進(jìn)行初始化和對發(fā)送和接收部分進(jìn)行設(shè)置,以便進(jìn)行串口的通信)

評論