基于S3C2410A設計的工程地震儀方案

3.2 硬件介紹

3.2.1 協處理器模塊

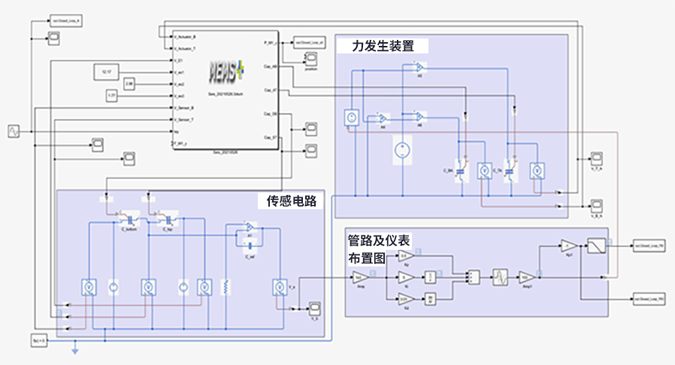

系統的協處理器采用Xilinx公司的FPGA,型號為SPARTANIIE XC2SIOOE。該芯片共有2700個邏輯單元,10萬個邏輯門,片內塊RAM為40KB。其具體實現以下功能:

· A/D模塊讀/寫時序控制;

· 生成FIFO,其主要功能是存儲經A/D編碼的數據:

· 提供ARM處理器控制信號。

FPGA芯片分4部分來實現上述功能:

(1)內部控制信號產生器

FPGA對50 MHz時鐘分頻產生A/D芯片采樣時鐘Sampleclk和ARM處理器外部時鐘Sysclk;Sysclk經鎖相環電路(PLL)后產生ARM處理器工作所需的時鐘信號 。

(2)ARM控制器

提供ARM處理器正常工作所必須的各種控制信號;實現ARM處理器地址總線、數據總線和外部中斷信號接入 。

(3)A/D控制器

控制A/D模塊的數據轉換。產生A/D轉換起始信號(/HOLD),檢測數據轉換完成信號(/EOC),產生FIFO寫入信號,實現數據轉換通道選擇。

(4)FIFO存儲器

生成FIFO,完成A/D轉換數據的存儲。

3.2.2 ARM處理器模塊

ARM 處理器模塊由FLASH、SDRAM 和s3C2410共同構建。系統選用Samsung公司的K9F1208UOA構建8位FLASH 存儲器系統。K9F1208UOA單片容量為64 MB;選用兩片單片容量32 MB。數據寬度為16位HY57V561620CT,并聯構建32位SDRAM存儲器系統,共64 MB的SDRAM空問可以滿足嵌入式操作系統和各種復雜算法的運行要求。ARM處理器對各模塊的控制則是通過底層驅動控制協處理器FPGA產生各種控制信號來實現。

3.2.3 預處理和A/D模塊

傳感器傳播的模擬信號比較微弱,需要經過前置放大等預處理后方具備數據有效性。預處理主要是由前置放大電路構成,A/D模塊主要由模擬開關和A/D轉換芯片構成。模擬開關采用AD公司的AD7506,可實現12通道數據采集。A/D轉換芯片采用CIRRUS公司的CS5381,是120dB、192kHz高性能立體聲24位Σ 一△ A/D變換器,內置雙極性電路構成的混合集成轉換顯片,具有外接元件少,功耗低,精度高等特點,并且具有自動校零和自動極性轉換功能,只需外接少量的阻容件即可構成一個完整的A/D轉換器。

3.2.4 接口和顯示模塊

包括常用的接口和顯示器件。接口包括常用的串口等,用以進行數據的外部存儲。顯示模塊主要包括構成操作的LCD和觸摸屏等外圍顯示設備。

4 嵌入式系統軟件設計

軟件部分分為FPGA控制程序和ARM處理器兩部分,FPGA用VHDL來設計,基于s3C2410A的軟件設計主要任務有數據采集的驅動程序,操作系統的移植以及上層應用軟件的設計。嵌入式操作系統應用WinCe.net,上層應用軟件開發使用Em-bedded Visual C++,底層驅動和ARM處理器的調試則使用c語言。

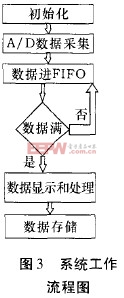

系統開始工作后ARM處理器和FPGA協處理器中的FIFO開始初始化。經A/D轉換后的數據存入對應的FIFO中。FIFO中的數據容量達到一定限度即產生巾斷,ARM處理器中的主程序產生中斷等待線程;一旦中斷產生則進入中斷服務程序,讀取數據,之后進入ARM系統進行相應的處理,然后存儲到存儲設備。如圖3所示。

評論