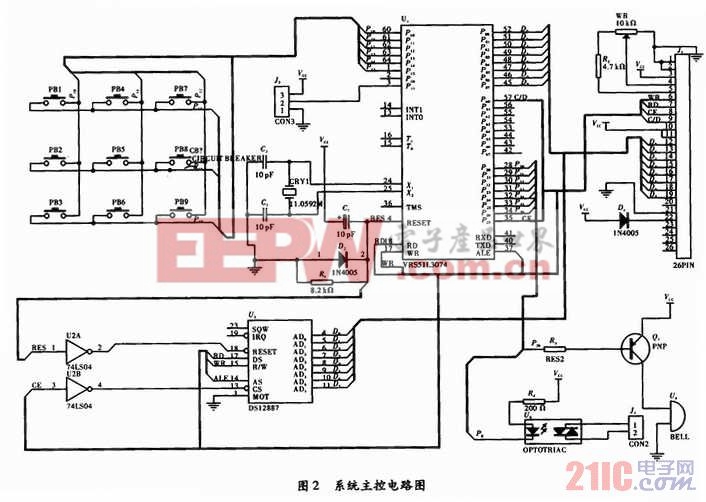

基于VRS51L3074的多點定鬧電子日歷鐘的設計

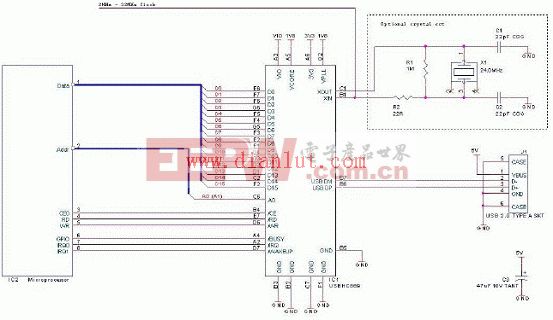

采用VRS51L3074單片機作為控制核心對時鐘芯片DSl2887進行控制,讀取時間,提取數(shù)據(jù),對輸入信號進行處理,最后通過LCD顯示各種時間、日歷及鬧鐘信息,從而實現(xiàn)整個設計的控制功能。系統(tǒng)主控電路如圖2所示。VRS51L3074片內(nèi)自帶40 MHz振蕩器,可無需外部晶振為系統(tǒng)提供時鐘信號。通過對時鐘主電路之間預分頻器的配置可靈活設置系統(tǒng)時鐘以滿足不同應用的需要。系統(tǒng)時鐘源選擇及分頻比設置由特殊功能寄存器DEVCLKCFGl和DEVCLKCFG2控制。

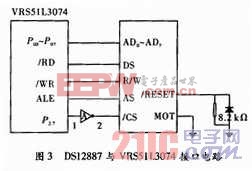

3.1 單片機與DSl2887時鐘芯片的接口設計界面

單片機與DSl2887時鐘芯片的接口界面如圖3所示。兩者之間要實現(xiàn)同步通信,就需要用到6個口線:(1)復位/RESET。(2)I/O數(shù)據(jù)線。(3)片選信號線/CS。(4)數(shù)據(jù)激發(fā)或讀取線DS。(5)讀取/寫入,輸入線R/W。(6)地址激發(fā)輸入線AS。

在以上6個口線中,DS、R/W都有兩種操作模式。本設計采用Intel總線時序,故MOT腳接地。在這種模式下,DS(數(shù)據(jù)激發(fā)或讀取)腳稱為/RD 腳。AD0~AD7是多工雙向的地址/數(shù)據(jù)總線。在總線周期的第一段時間呈現(xiàn)的是地址,同樣的IC腳和信號路徑,在第二段時間當成數(shù)據(jù)使用。因總線從地址到數(shù)據(jù)的改變是發(fā)生在內(nèi)部SRAM的存取時間,所以地址/數(shù)據(jù)作成多工形態(tài)并不會使DSl2887的存取時間變慢。片選信號線/CS選擇輸入為LOW時,即可對DSl2887進行存取,在總線周期即使沒有使能/CS腳,也同樣會鎖存住地址但沒有存取的動作發(fā)生。當Vcc 4.25 V時,DSl2887會除能/CS腳,禁止存取動作,此功能會保護在電源消失期間的即時時鐘和SRAM里的數(shù)據(jù)。地址激發(fā)輸入AS送一個正向地址激發(fā)脈沖到輸入腳,然后在AS/ALE的下降邊緣使得地址栓在DSl2887內(nèi)。在下一個時鐘下降沿,地址激發(fā)輸入將清除,而不管片選端/ CS是否置位。接入命令必須成對發(fā)送。/RESET腳的信號對于時鐘、日歷或SRAM都沒有影響。在電源上升時,RESET腳應該維持在LOW一段時間,以便允許電源電壓穩(wěn)定下來,/RESET腳維持在LOW的時間視應用而定。

評論