基于AVR單片機的ISP1362OTG設計

0 引言

本文引用地址:http://www.104case.com/article/173045.htm隨著PDA、移動電話、數碼相機、打印機等消費類產品的普及,用于這些設備與電腦、或設備與設備之間的高速數據傳輸技術越來越受到人們的關注。以往以計算機為核心的數據傳輸結構,非常不利于USB,總線在嵌入式行業的應用,也不適用于野外作業,而OTG技術的推出則可實現在沒有PC的情況下,設備與設備之間的數據傳輸,它拓展了USB技術的應用范圍。本文采用的設計方案是基于Philips公司的ISP1362 OTG控制芯片,參照最新的USB OTG技術規范,設計了一種遵循USB協議的主/從機系統。

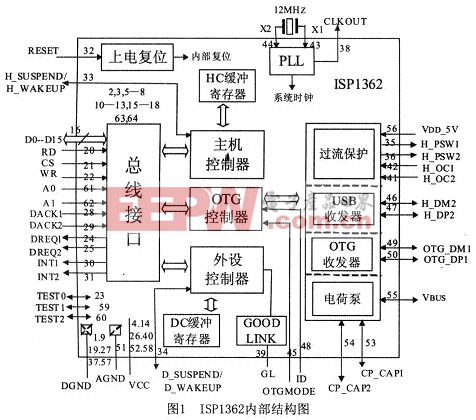

1 ISP1362芯片的內部結構

Philips公司的ISP1362是一款符合USB 2.0總線協議的接口芯片,內部有3個USB控制器一主機控制器、設備控制器和OTG控制器。其中,主機控制器具備高度優化的USB主機功能;設備控制器則具有多達14個可編程端點,又可以被配置成雙緩沖端點進一步提高吞吐量:而OTG控制器主要提供包括監控和轉換功能在內的所有OTG控制。ISP1362內部構造如圖1所示。

2 USB OTG主/從機系統設計

USB OTG主/從機系統設計包括硬件設計和軟件設計兩大模塊。其中硬件電路主要是USB接口電路板的設計;軟件設計包括設備初始化、系統的功能設計、設備驅動程序設計等,下面分別介紹系統軟、硬件系統的設計方法。

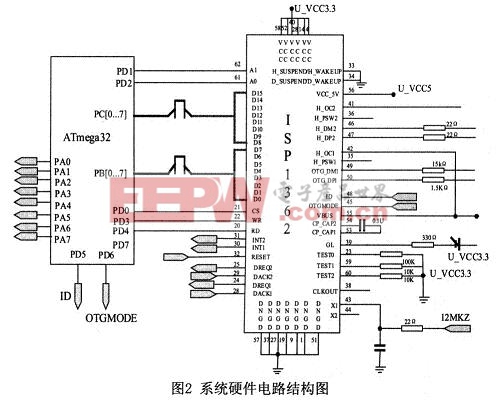

2.1 系統硬件電路設計

USB OTG主/從機設計的硬件電路如圖2所示,圖中ATmega 32的PD口和IPA口用于控制ISP1362的時序,PB口和PC口則用于與ISP1362的D[0..15]進行數據交換。ISP1362芯片有Port1和IPort2兩個USB接口。Port1是個綜合接口,可以配置成downstream、upstream或者是OTG;Port2是作為固定的downstream,主要接一般的USB設備。當ISP1362做主機時,主機內部的寄存器通過檢測其相應狀態寄存器的值就可以判斷是Port1還是Port2接了設備,從而進行相應的處理。

ISP1362的Port1口主/從機功能通過ID、OTGMODE兩引腳電平的高低組合來確定。當OTGMODE引腳接低,無論ID電平如何,則芯片的Port1口只能OTG用;如果OTGMODE接高,ID接低,芯片的Port1口作主機使用;OTGMODE接高,ID也接高時,則芯片的Port1口作外設使用。在電路中通過15kΩ的上拉電阻和下拉電阻實現ID、OTGMODE兩引腳電平的高低變化。

2.2 系統軟件設計

本設計的主機系統是一個軟件和硬件的集合體,功能的實現不依賴于任何操作系統,而是通過中斷來調度各個任務,使之滿足USB通信的要求,因此系統是按照協議規范和特定的時序運行的。

本系統是ISP1362工作于主/從機模式下的應用,按系統硬件電路配置完成接口芯片,然后對其編程,就可以進行USB數據傳輸。系統工作流程如下:首先進行系統初始化,構建PTD傳輸描述符,接著總線枚舉過程,給外設分配地址,獲取外設的基本信息,并判斷外設為主機設備或是從機設備,之后驅動相應的主/從機驅動程序運行,數據傳送和接收,根據總線的活動情況判斷是否掛起。系統流程圖如圖3所示:

評論