MSP430x4xx系列微控制器的獨(dú)特時(shí)鐘設(shè)計(jì)

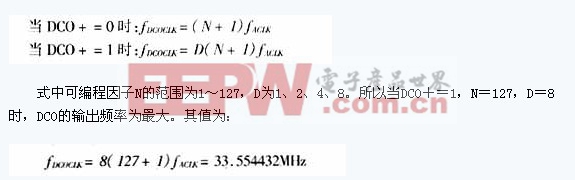

式中,fACLK取32768Hz。可見(jiàn),通過(guò)改變N、D和DCO+,可以很容易地調(diào)節(jié)用作MCLK/SMCLK的DCO頻率。但要注意,最后得到的MCLK不能超過(guò)器件的工作頻率。

3.2頻率抽頭

DCO的輸出時(shí)鐘為DCOCLK,這個(gè)時(shí)鐘被(D×(N+1))分頻后應(yīng)與ACLK進(jìn)行比較。若DCOCLK用于系統(tǒng)時(shí)鐘MCLK,則同步器將對(duì) ACLK和MCLK/(D×(N+1))進(jìn)行比較,然后用比較所得的差值來(lái)對(duì)一個(gè)10位的頻綜器進(jìn)行“up”或者“down”模式計(jì)數(shù)。這樣, MCLK/SMCLK就可以在1024種可能的設(shè)置上不斷地進(jìn)行調(diào)節(jié)。一旦頻率被鎖定,同步器輸出的誤差信號(hào)就變?yōu)?,此時(shí)有MCLK=N×ACLK。在頻綜器的10位輸出中,5位用于DCO頻率抽頭(NDCO),另外的5位用于頻率調(diào)整(NDCOMOD)。5個(gè)抽頭可組成29種頻率(28,29,30和31抽頭是一樣的),每一個(gè)抽頭比前一個(gè)要高約10%。

明顯可以看到:DCO只能產(chǎn)生一些離散的頻率分量。所以說(shuō)僅僅依靠改變N、D和DCO+無(wú)法使同步器的輸出達(dá)到嚴(yán)格的0。

3.3頻率調(diào)整

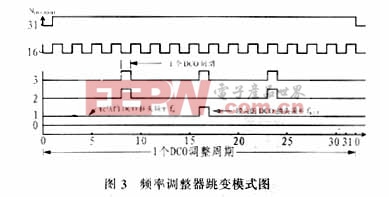

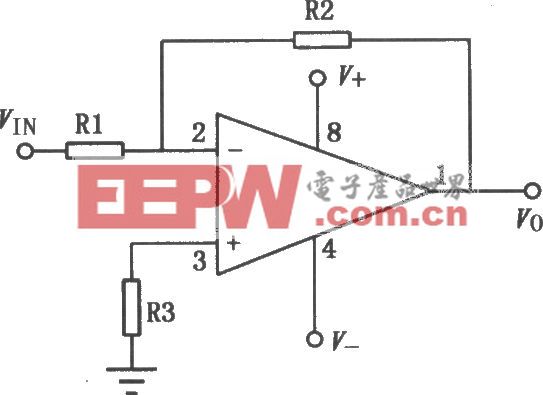

DCO頻率調(diào)整器的作用是通過(guò)混合相鄰的DCO周期來(lái)減小長(zhǎng)期的累計(jì)周期變化。換句話(huà)說(shuō),就是通過(guò)控制fn+1在一個(gè)調(diào)整周期內(nèi)所占的比率來(lái)減小輸出頻率與所需頻率之間的誤差。具體的頻率調(diào)整器跳變模式如圖3所示。圖中,調(diào)整器以32個(gè)DCO時(shí)鐘周期為一個(gè)周期。NDCOMOD可用于定義需要混合的fn+1的比例常數(shù)。

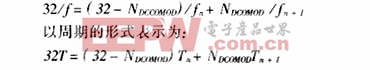

下面的公式定義了DCO長(zhǎng)期輸出頻率與相鄰跳變頻率之間的關(guān)系:

由此可見(jiàn),頻率調(diào)整器通過(guò)為每個(gè)DCO周期獨(dú)立地選擇fn或者fn+1,來(lái)調(diào)整DCO的輸出頻率,進(jìn)而實(shí)現(xiàn)分?jǐn)?shù)抽頭的目的。

評(píng)論