采用段式管理的大容量外部RAM擴展技術

1.3.2 邏輯段表設計與段的存取管理

為了便于對段的存取管理控制,設計一個邏輯段表,表的內(nèi)容為邏輯段號。因為1個邏輯段為64KB,它與2個物理段(每段32KB)相對應,因而邏輯段表示的長度為實際物理段總數(shù)的一半。設有N個段,邏輯段表如圖3所示。例如:有8個32KB的物理段,邏輯段表的長度為4B,邏輯段表的內(nèi)容為:0,1,2, 3。實際的物理段號為:0,1,2,3,4,5,6,7。每個邏輯段號與2個物理段號相對應。

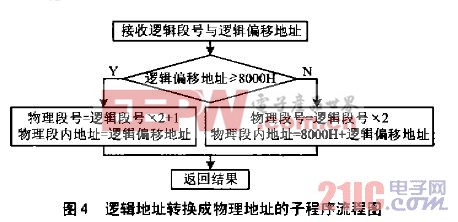

另外,為了便于存取控制,設計一個將邏輯地址自動轉(zhuǎn)換成物理地址的子程序,子程序必須簡單。經(jīng)過分析,把每個32KB的物理段的起始地址都設為8000H,即每個32KB的物理段的段內(nèi)地址都是從8000H~0FFFFH。根據(jù)邏輯地址與物理地址的對應關系,筆者設計了一個子程序,由于結(jié)構簡單,只給出具體流程圖,如圖4所示。子程序的入口參數(shù)為邏輯段號與邏輯偏移地址,返回結(jié)果為物理段號與物理段內(nèi)地址。這樣,對段的存取訪問可先查邏輯段表查出邏輯段號,再調(diào)用該子程序?qū)崿F(xiàn)。

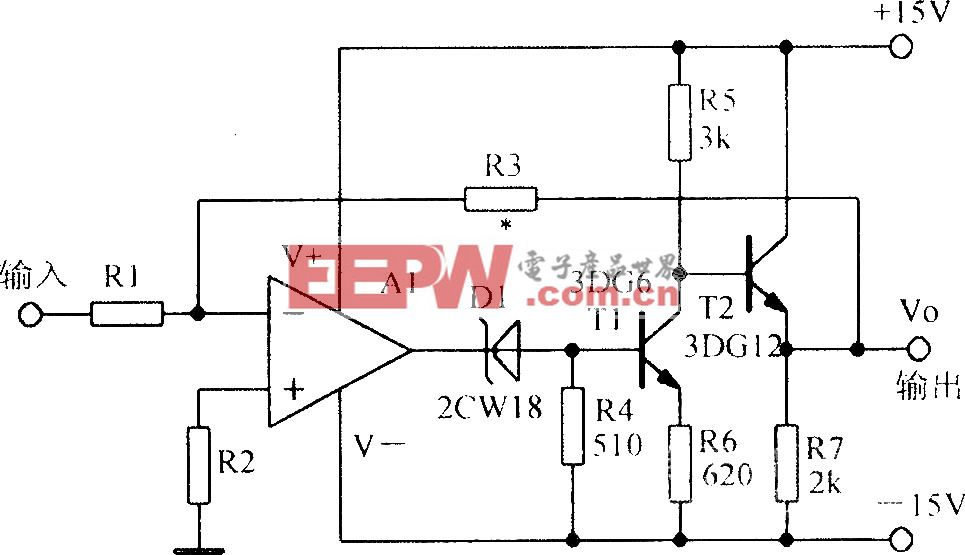

分析:由于地址空間為128KB,因此可以設置4個大小同為32KB的段,每段選用1個62256芯片。電路原理分析:8096的P3口輸出直接作為數(shù)據(jù)總線使用,同時外接74LS373的輸出,作為低地址總線A0~A7;P4口的P4.0~P4.6作為高地址總線A8~A14使用,P4.7經(jīng)過一反相器連接74LS139(雙2~4譯碼器)的1G(使能器);P1.1、P1.0分別與74LS139譯碼器的兩個輸入端1A1、1A0相接。P1.1、 P1.0、P4.7分別作為高地址總線A17、A16、A15使用。譯碼器的輸出1Y3、1Y2、1Y1、1Y0分別與4個寄存器62256的片選信號 CS相接。這樣可以得出:段0存儲器的物理地址為08000H~0FFFFH,段1存儲器的物理地址為18000H~1FFFFH,段2存儲器的物理地址為28000H~2FFFFH,段3存儲器的物理地址為38000H~3FFFFH;而邏輯地址為00000H~1FFFFH。邏輯段表的內(nèi)容為0、1,具體電路如圖5所示。

評論