基于ARM的快速原型化平臺的方案

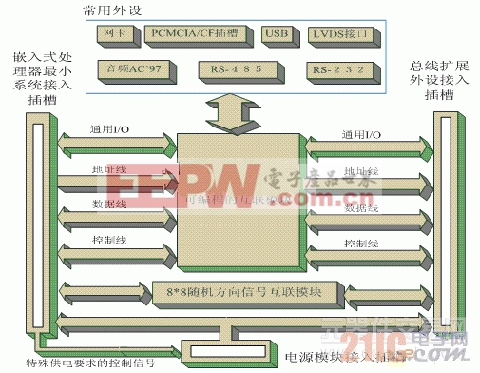

圖2是基于ARM核處理器的嵌入式系統的框圖。該系統分成兩個部分,一部分是最小系統,由嵌入式ARM核處理器和存儲器組成;另外一部分包括從嵌入式處理器片內外設接口直接擴展的外設和通過總線擴展的外設。為了充分利用模塊化設計方法,這些部分應該能夠通過靈活的互連組成一個平臺。靈活的互連功能由互連模塊完成。

可編程器件如CPLD和FPGA,可以在系統編程,修改連接只需要修改相應的控制程序即可,非常方便靈活。CPLD成本低,運行速度快,但是集成度比較低。FPGA集成度高,可以實現CPLD很難實現的復雜的邏輯功能,例如內嵌邏輯分析儀程序,獲取必要的信號,完成系統在線測試。FPGA另外一個優勢就是可以動態配置,例如系統上電時配置自檢程序,自檢通過后再配置實際工作的程序。最后,在FPGA里面嵌入CPU軟核,進行SOC的開發。所以可編程互連模塊選用FPGA來組成。

為了確定可編程互連模塊的插入位置,再來分析圖2嵌入式系統的結構。

最小系統決定了整個系統的處理能力,是整個系統的核心。常用的嵌入式處理器的時鐘周期已經高達400MHz,并且會進一步發展。連接處理器的總線速度和存儲器芯片的速度也超過了100MHz。FPGA引腳到引腳的延時是幾個納秒的數量級,所以FPGA模塊的插入會降低整個系統的處理速度。故在處理器和存儲器之間不能插入FPGA模塊。外設可以使得嵌入式系統和實際應用環境進行通信和交互操作。通常外設已經高度模塊化并且相互獨立,在外設之間幾乎不會有柔性連接的要求,而且處理器和外設之間的數據通信速度比最小系統的運行速度要慢很多。因此,用互連模塊取代最小系統和外設之間的直接物理連接是切實可行的。

圖3中,可編程互連模塊是快速原型化平臺的核心部分。常用的外設部分包括:網卡,USB接口,LVDS接口,RS-232接口,RS-485接口,音頻AC`97接口,PCMCIA/CF卡接口。這些常用外設就是前文提到的可重復利用的模塊。由于嵌入式處理器的總線、通用I/O、專用I/O和各種外設都連接在可編程互連模塊上,因此不同的嵌入式處理器只需要設計最小系統即可,然后將該最小系統接入快速原型化平臺,利用這個平臺提供的外設進行系統調試。

以上設計的快速原型化平臺,不僅考慮了當前嵌入式硬件系統的發展特點即嵌入式處理器種類多,外設種類相對較少,接口標準趨于統一,同時又充分體現了可測性、靈活性、模塊化的設計思想。

3 隨機方向信號的可配置互連

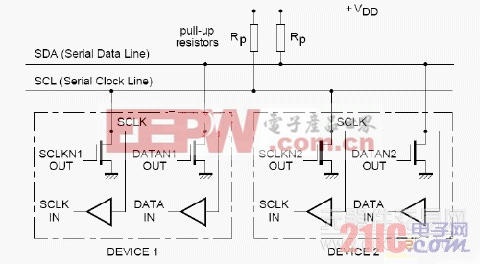

常見的信號傳輸方向不管是單向的還是雙向的,都可以預先確定。例如,數據總線是雙向的,讀或者寫是完全確定的,可以通過讀寫信號來控制數據的傳輸的方向。但是有一類特殊的總線,例如I2C,它是多主/從的通信總線。如圖4所示,如果設備1發起通信,則SCL上的信號傳輸方向是從設備1到設備2,如果是設備2作主設備發起通信,則SCL的上的信號傳輸方向剛好相反。系統設計中要求總線上可以雙向傳輸信號。FPGA內部由一系列的邏輯門組成,如果I2C 信號通過FPGA來連接的話,就不能正常工作。這是因為,雙向傳輸可以等效視為由兩個反并聯的門來實現(如圖5,用方向控制信號來確定實際的傳輸方向)。但是,I2C信號,沒有明確的方向控制信號,也就無法正確地通過圖5 所示結構的電路。

圖4(I2C總線)

評論