基于FPGA和51單片機信號發生器設計與實現

1.1.2 C8051F0201簡介

C8051F0201(以下簡稱51單片機)器件是完全集成的混合信號系統級MCU芯片,具有32個數字I/O引腳。此款51單片機具有高速、流水線結構的8051兼容的CIP-51內核(可達25 MIPS)。全速、非侵入式的在系統調試接口(片內)。12位、100 ksps的8通道ADC,帶PGA和模擬多路開關。8位500 ksps的ADC,帶PGA和8通道模擬多路開關兩個12位DAC,具有可編程數據更新方式。64 K字節可在系統編程的FLASH存儲器。4 352(4 096+256)字節的片內RAM,可尋址64 k字節地址空間的外部數據存儲器接口。硬件實現的SPI、Sm Bus/I2C和兩個UART串行接口,5個通

用的16位定時器。具有5個捕捉/比較模塊的可編程計數器/定時器陣。列片內看門狗定時器、VDD監視器和溫度傳感器,每個MCU都可在工業溫度范圍(-45~+85℃)內用2.7~3.6 V的電壓工作。端口I/O、/RST和JTAG引腳都容許5 V的輸入信號電壓。

1.2 C8051單片機軟件設計

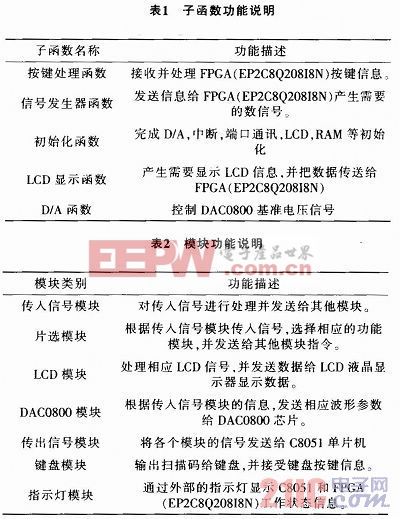

C8051單片機軟件主要包括按鍵處理函數、信號發生器控制函數、初始化函數、LCD顯示函數、D/A函數以及主函數。軟件設計的主程序流程框圖如圖3所示,子函數詳細功能如表1所示。本文引用地址:http://www.104case.com/article/171350.htm

1.3 FPGA(EP2C8Q20818N)軟件設計

本文中主要采用Verilog HDL語言設計。主要包括片選模塊、時鐘驅動模塊、鍵盤掃描模塊、傳出信號模塊、LCD模塊、DAC0800模塊以及指示燈模塊。詳細功能如表2所示。

評論