與MCS51系列單片機相同的數據存儲器擴展技術解析方案

1.3.2 邏輯段表設計與段的存取管理

為了便于對段的存取管理控制,設計一個邏輯段表,表的內容為邏輯段號。因為1個邏輯段為64KB,它與2個物理段(每段32KB)相對應,因而邏輯段表示的長度為實際物理段總數的一半。設有N個段,邏輯段表如圖3所示。例如:有8個32KB的物理段,邏輯段表的長度為4B,邏輯段表的內容為:0,1,2, 3。實際的物理段號為:0,1,2,3,4,5,6,7。每個邏輯段號與2個物理段號相對應。

另外,為了便于存取控制,設計一個將邏輯地址自動轉換成物理地址的子程序,子程序必須簡單。經過分析,把每個32KB的物理段的起始地址都設為8000H,即每個32KB的物理段的段內地址都是從8000H~0FFFFH。根據邏輯地址與物理地址的對應關系,筆者設計了一個子程序,由于結構簡單,只給出具體流程圖,如圖4所示。子程序的入口參數為邏輯段號與邏輯偏移地址,返回結果為物理段號與物理段內地址。這樣,對段的存取訪問可先查邏輯段表查出邏輯段號,再調用該子程序實現。

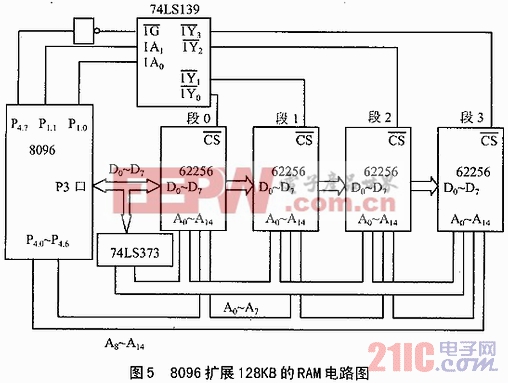

2 設計舉例:8096擴展128KB的RAM

分析:由于地址空間為128KB,因此可以設置4個大小同為32KB的段,每段選用1個62256芯片。電路原理分析:8096的P3口輸出直接作為數據總線使用,同時外接74LS373的輸出,作為低地址總線A0~A7;P4口的P4.0~P4.6作為高地址總線A8~A14使用,P4.7經過一反相器連接74LS139(雙2~4譯碼器)的1G(使能器);P1.1、P1.0分別與74LS139譯碼器的兩個輸入端1A1、1A0相接。P1.1、 P1.0、P4.7分別作為高地址總線A17、A16、A15使用。譯碼器的輸出1Y3、1Y2、1Y1、1Y0分別與4個寄存器62256的片選信號 CS相接。這樣可以得出:段0存儲器的物理地址為08000H~0FFFFH,段1存儲器的物理地址為18000H~1FFFFH,段2存儲器的物理地址為28000H~2FFFFH,段3存儲器的物理地址為38000H~3FFFFH;而邏輯地址為00000H~1FFFFH。邏輯段表的內容為0、1,具體電路如圖5所示。

3 總結

這種段式管理的數據存儲器擴展技術簡單方便,具有很大的優越性,具體體現在以下幾方面:從應用角度看,此技術能夠實現大容量的數據存儲器的擴展,數據存儲器可采用RAM、EEPROM、FLASH RAM等;最大的擴展容量為8MB,遠遠超出了一般應用系統的數據存儲器擴展需求。從用戶角度看,用戶在編程時不必考慮實際物理數據存儲器的地址空間是否連續,通過段式管理,使用連續的邏輯地址來編程,克服了不連續物理地址空間的缺陷,而且,對各段存儲的數據提供了保護;在一般的大數據量的單路信號檢測與處理系統中,此技術使得用戶對連接采集數據的存取是透明的,不受硬件的局限,便于用各種高級語言開發設計。從硬件角度看,對于數據存儲器采用多個32KB 的RAM芯片,各存儲段相互獨立,互不影響,各段的存儲器芯片的故障也不會對整個系統造成很大影響;在一般的多數大數據量的信號檢測與處理系統以及由單片機組成的集散式控制系統中,可以為每路采集的數據分酌情不同的段來存儲,這樣對各段存儲的數據提供了保護,提高了整個系統的可靠性,應用效果是非常理想的。對于數據存儲器采用單個大容量的EEROM或FLASH RAM芯片時,硬件電路更為簡單,不需要譯碼器等電路。

評論