基于串口通信的單片機仿真和C語言開發

1)先將數據線置高電平1;2) 延時(該時間要求不是很嚴格,但是要盡可能短一些);3) 數據線拉到低電平0;4) 延時 750us(該時間范圍可以在480~960us);5) 數據線拉到高電平1;6)延時等待。如果初始化成功則在15~60ms內產生一個由DS18B20 返回的低電平0,據該狀態可以確定它的存在。但是要注意,不能無限地等待,不然會使程序進入死循環,所以要進行超時判斷;7) 若 CPU 讀到數據線上的低電平0 后,還要進行延時,其延時時間從發出高電平算起最少要480us;8)將數據線再次拉到高電平后結束。

2. DS18B20 寫數據

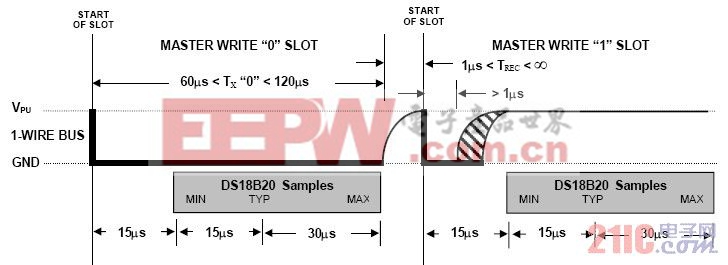

圖3.3 寫數據時序圖

1) 數據線先置低電平0;

2)延時確定的時間為15us;

3) 按從低位到高位的順序發送數據(一次只發送一位);

4) 延時時間為 45us;

5) 將數據線拉到高電平1;

6) 重復 1)到5)步驟,直到發送完整個字節;

7)最后將數據線拉高到1.

3. DS18B20 讀數據

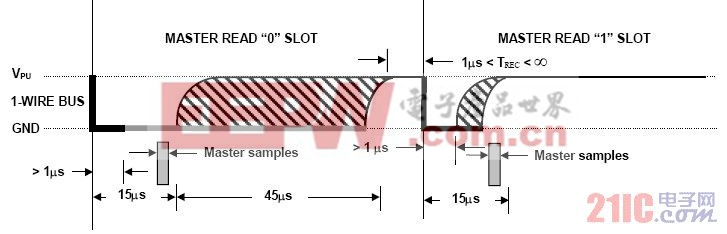

圖3.4 讀數據時序圖

1)將數據線拉高為1;

2) 延時 2us ;

3) 將數據線拉低0 ;

4) 延時 6us ;

5) 將數據線拉高1 ;

6)延時 4us ;

7) 讀數據線的狀態得到1 個狀態位,并且進行數據處理;

8) 延時 30us ;

9) 重復 1)到7)步,知道讀取完一個字節。

4 硬件設計

4.1 時鐘電路及復位電路

1.時鐘電路

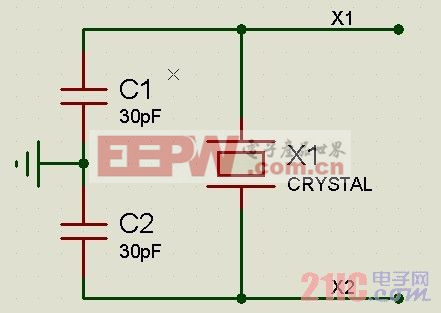

時鐘電路可以產生CPU 校準時序,是單片機的控制核心,本次設計是通過外接12MHz的晶振來實現時鐘電路的時序控制。在使用片內振蕩器時,XTAL1 和XTAL2 分別為反向放大器的輸入端和輸出端。外接晶體以及電容C3 和C5 構成并聯諧振電路,接在放大器的反饋回路中。當用外部時鐘驅動時,XTAL2引腳應懸空,而由XTAL1引腳上的信號驅動,外部振蕩器通過一個2 分頻的觸發器而成為內部時鐘信號,故對外部信號的占空比沒有什么要求,但最小和最大的高電平持續時間和低電平持續時間應符合技術要求。電路如圖4.1 所示。

圖 4.1 晶振電路

評論