兼容51指令的8位MCU IPCORE設計

1 前言

本文引用地址:http://www.104case.com/article/170741.htm當前,在微電子及其應用領域正在發生一場前所未有的變革,這場變革是由片上系統(SOC)技術研究應用和發展引起的.從技術層面看SOC技術是超大規模集成電路發展的必然趨勢和主流,它以超深亞微米VDSM(Very Deep Submicon)工藝和知識產權IP核復用技術為支撐。在眾多的IP核中,MCU CORE以其在SOC中嵌入后能充分發揮其處理靈活、軟件可升級、硬件開銷少的特點,在很大程度上成為SOC芯片必需模塊。INTEL公司的MCS-51系列MCU 可以說是目前國內應用時間最長、最普及、可獲得應用資料最多的功能強大的8位MCU , 所以建立兼容51指令MCU可綜合IP核對于各種嵌入式系統和片上系統(SOC)的應用具有重要意義。

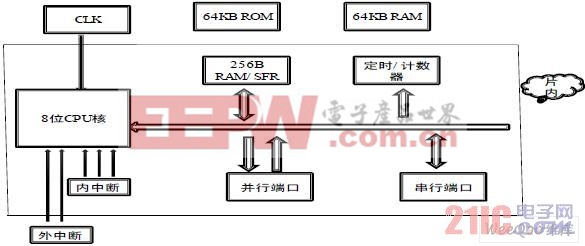

圖1 IPCORE 內部結構

2 總體構架設計

本設計采用自頂向下的設計方法成功設計了與MCS-51 系列微處理器指令集完全兼容的8位嵌入式MCU核, 此核的內部結構如圖1所示(整個設計過程也是圍繞其產開)。

3 核內單元(主要單元設計的概述)

3.1 ALU 單元的設計:

ALU單元由一些基本操作功能模塊(加/減法模塊、乘法模塊、除法模塊、十進制調整模塊和邏輯模塊)構成,整個操作是通過多路選擇器來完成的。在ALU單元的結構上,將乘、除法單元各自獨立出來完成算術運算指令中的乘、除法運算。這樣可以回避傳統典型微處理器基于累加器ACC的ALU結構,并且由于ALU單元被設計成純組合邏輯,因而速度較快,從而提高算術運算指令的執行效率。

3.2 時序設計

主要從簡化控制器設計、提高核的性能出發,本設計沒有采用Intel MCS-51雙相時鐘的復雜時序設計,而是采用單相時鐘(單相時鐘因為在時序和傳輸上比較簡單可靠,被一些高性能芯片使用)、全同步設計,所有時序電路均采用邊沿觸發的觸發器。采用單相時鐘全同步設計會使芯片面積有所增加,但降低了設計的復雜度,減少了生產工藝不確定性對系統性能的影響,提高了設計的成功率。

3.3 控制單元的設計

控制器本質上是一個結構及狀態轉移非常復雜的有限狀態機(FSM)。從程序執行的宏觀角度看,每一條指令對應著這個復雜的有限狀態機的一個狀態,一條一條指令的依次執行,就是一系列狀態轉移。控制器的實現主要有兩種:硬布線實現方式和微程序實現方式。考慮到本次設計的是一個用于SOC的IP核所以采用PLA技術,就是用存儲技術實現硬布線邏輯,可以認為它是硬布線邏輯控制器和微程序控制器兩者的折衷方案。由于PLA微控制器集中了硬布線邏輯控制器與微程序控制器兩者的優點,與硬布線邏輯控制器相比,它的設計工作量小,修改、維護都比較方便。與微程序控制器相比,它的速度較快。這些優點都適合其作為內核整合在SOC中。為了提高FSM的效率,我們把控制單元中組合邏輯和時序邏輯分開設計,組合邏輯主要輸出控制信號并且產生次態邏輯,時序邏輯主要實現存儲單元的讀寫。

評論