Cortex-M3內核的異常處理機制及其新技術研究

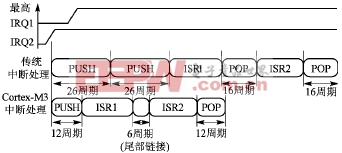

CortexM3和ARM7在處理遲到高優先級異常時的差異如圖6所示。

當IRQ2正在為執行ISR2保存處理器狀態時,遲到了一個優先級更高的異常IRQ1.這時ARM7繼續進行壓棧操作。在壓棧操作完成后,ARM7繼續為執行ISR1進行壓棧操作,然后執行ISR1.其實,兩次壓棧操作所保存的內容是一樣的。因此,CortexM3對這個階段的操作進行了優化,引進了遲到異常技術,只進行一次的壓棧操作。并且在ISR1執行完成之后,CortexM3沒有進行出棧操作,而是通過一個6周期的尾鏈,直接進入ISR2的執行。

圖6 NVIC對遲到的具有更高優先級異常的響應

在上面的例子中,ARM7處理器的異常開銷:

CortexM3處理器的異常開銷:

其中,TARM7_later和TM3_later分別為ARM7和CortexM3處理遲到異常所用的時間開銷;Ttailchaining為CortexM3處理尾鏈所用的時間。

通過計算可以看出,CortexM3少用了44周期,節省65%的異常開銷。

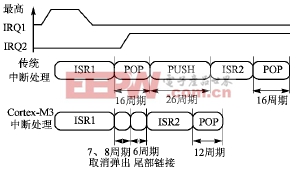

3.3 處理器處理backMtoMback異常

若一個新的異常在上一個異常寄存器出棧時到來,ARM7和CortexM3的處理方式也有很大不同。CortexM3和ARM7在處理 backMtoMback異常時的差異如圖7所示。ARM7繼續當前的出棧操作,在出棧操作完成后,處理器為執行ISR2進行壓棧操作,然后執行 ISR2.其實,這時候處理器出棧和壓棧的內容是一致的。CortexM3同樣優化了這個階段的操作,引進了尾鏈機制。當IRQ2到來時,CortexM3立即中止已經進行了8個周期的出棧操作,轉而進行尾鏈操作,然后執行ISR2.

圖7 NVIC搶占出棧

在處理backMtoMback異常時,ARM7處理器用在ISR1到ISR2轉換的異常開銷:

CortexM3處理器用在ISR1到ISR2轉換的異常開銷:

其中,TARM_btb和TM3_btb分別為ARM7和CortexM3處理backMtoMback異常轉換所用的時間開銷;Tcancel為發生尾鏈時CortexM3已用于狀態恢復的時間。

通過計算可以看出,CortexM3少用了28周期。其實,CortexM3處理器用在ISR1到ISR2轉換的異常開銷最低可以優化到只用6個周期, 這樣就極大地提高了backMtoMback異常的響應能力。

結語

本文闡述了CortexM3處理器的異常處理機制。通過和ARM7進行比較,量化分析了CortexM3在異常處理方面的優勢,對工程師使用CortexM3的異常處理會有一定參考和幫助。

評論