STM32-F2系列微控制器全方位解決方案詳細闡釋

引言

本文引用地址:http://www.104case.com/article/170479.htm工業(yè)環(huán)境正在對嵌入式控制系統(tǒng)開發(fā)人員構(gòu)成日益嚴峻的挑戰(zhàn),究其主要原因,當(dāng)前系統(tǒng)和通信協(xié)議棧變得越來越復(fù)雜,系統(tǒng)實時性和安全要求越來越嚴格,同時,這種趨勢直接影響到半導(dǎo)體元器件的特性和技術(shù)規(guī)格。

為克服這些挑戰(zhàn),意法半導(dǎo)體在今年初發(fā)布了STM32-F2系列微控制器,以幫助開發(fā)人員實現(xiàn)要求苛刻的工業(yè)應(yīng)用。新系列產(chǎn)品誕生于深受市場歡迎的STM32產(chǎn)品家族,擁有更高的性能、更大的存儲容量和針對工業(yè)應(yīng)用優(yōu)化的外設(shè)。F2系列產(chǎn)品在一顆芯片上集成了多種功能,例如,控制/調(diào)整功能和復(fù)雜的通信協(xié)議棧。高集成度的優(yōu)點是,縮小印刷電路板空間,避免在不同的控制器之間存在易受到電磁兼容性影響的連接電路,優(yōu)化應(yīng)用成本。

工業(yè)自動化市場的特點是多個通信協(xié)議并存,實時應(yīng)用需要高效的操作系統(tǒng)。因此,軟件棧和操作系統(tǒng)成為選擇微控制器的首要參數(shù)。 STM32微控制器基于受到市場廣泛支持的Cortex M3內(nèi)核,因此,有20多家實時操作系統(tǒng)和通信協(xié)議提供商供用戶選擇。為使STM32微控制器更加完美,意法半導(dǎo)體還增加了一個兼容CMSIS的硬件抽象層和其它固件庫,例如,支持永磁同步電機(PMSM)的磁場定向控制 (FOC) 。本文將介紹兩個第三方專門為STM32F-2研發(fā)的工廠自動化軟件: IXXAT 開發(fā)的支持PTP的IEEE1588協(xié)議軟件包和 PORT 開發(fā)的Profinet通信協(xié)議棧。

STM32-F2針對工廠自動化的改進的性能

與上一代產(chǎn)品STM32-F1相比,STM32-F2在很多方面加以改進,特別是性能更加出色,外設(shè)接口更加豐富。STM32-F2采用90nm光刻技術(shù),處理速度達到120MHz,并使運行功耗保持在合理水平(300uA/MHz)。這項光刻技術(shù)的另一個好處是集成度更高,有助于降低應(yīng)用的系統(tǒng)級成本。

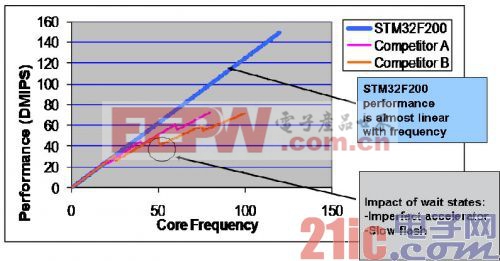

為了充分發(fā)揮Cortex-M3內(nèi)核的優(yōu)異性能,意法半導(dǎo)體重新評估了產(chǎn)品架構(gòu)。新產(chǎn)品在120MHz下釋放150DMIP的強勁性能(Dhrystone 2.1),CoreMark™測試成績?nèi)〉?54高分(2.120 CoreMark/MHz 通過EEMBC 認證), STM32F-2因而進入Cortex-M微控制器的第一陣營,這個成績歸功于自適應(yīng)實時存儲器加速器(ARTTM),采用這項閃存訪問管理技術(shù)后,應(yīng)用代碼執(zhí)行不再會受閃存本身固有的等待狀態(tài)的影響。雖然閃存的速度比內(nèi)核本身慢三倍,但是,在代碼執(zhí)行過程中不會出現(xiàn)等待狀態(tài),即便處理速度達到120MHz時也是零等待狀態(tài)。因此,新系列產(chǎn)品可大幅縮減設(shè)計尺寸,降低功耗和閃存的EMC影響,確保最高的產(chǎn)品性能。

STM32-F2的主要特性如下: 最高1MB的閃存、128kB RAM、6個UART(7.5Mbps)、3 SPI接口 (30Mbps)、支持IEE1588 PTP V2的以太網(wǎng)媒體訪問控制器(MAC)、4kB備用RAM、512字節(jié)的一次性可編程存儲器(OTP)。

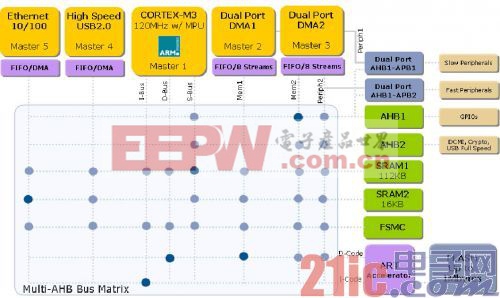

總線矩陣

除單純的內(nèi)核計算能力外,微控制器設(shè)計人員還必須考慮總線設(shè)計,在微控制器不同單元之間實現(xiàn)并行訪存和數(shù)據(jù)傳輸,例如,內(nèi)核和通信外設(shè)需要同時訪問不同的存儲器。因此,主要總線最終被設(shè)計成一個多層AHB總線矩陣,最多支持6個同步數(shù)據(jù)流。

STM32-F2系列微控制器共有5個總線主控制器:

· 有3條內(nèi)核總線的ARM Cortex-M3內(nèi)核

· 2個DMA控制器

· 高速 USB主設(shè)備控制器

· 10/100以太網(wǎng) MAC控制器

上圖中的黑點代表在這個7層總線結(jié)構(gòu)中總線主控制器與從控制器的全部接口。為提高系統(tǒng)的能效,SRAM存儲器被分成兩個存儲區(qū)SRAM1和SRAM2,SRAM1用于保存基本協(xié)議棧和變量,而SRAM2則用作通信外設(shè)的幀緩沖區(qū)。以太網(wǎng)和USB外設(shè)都占用了幾千字節(jié)的FIFO存儲空間,而且分別擁有一個各自專用的DMA控制器。

除多個SRAM分區(qū)外,該系統(tǒng)還有兩個AHB總線從控制器。同樣地,這樣的配置準許不同的總線主控制器并行處理和同步訪問不同的高速外設(shè),例如,加密處理器和通用輸入輸出端口。AHB從控制器和DMA控制器都是雙端口,這樣設(shè)計準許在AHB總線上直接連接DMA控制器與高速外設(shè),避免在總線矩陣和二級高速至低速橋上因延遲而降低性能。

外部存儲器接口又稱“靜態(tài)存儲控制器”,可直接連接不同的異步和同步存儲器、NOR/NAND閃存、SRAM、偽SRAM,甚至還能連接一個液晶顯示器控制器,外存接口總線頻率最高60MHz,還能通過指令總線(I-bus)獲取CPU內(nèi)核指令。

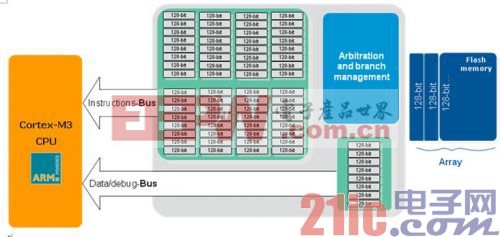

存儲器加速器

意法半導(dǎo)體的自適應(yīng)實時(ART)存儲器加速器(如上圖所示)可讓Cortex-M3內(nèi)核釋放最高的處理性能,雖然閃存本身需要等待狀態(tài),但是,引入這項技術(shù)后,STM32-F2以120 MHz的速度從閃存執(zhí)行代碼無等待狀態(tài)。

存儲器接口是128位寬,每次可取4-8條THUMB2指令。如果執(zhí)行線性代碼,因為預(yù)取指功能,即便閃存速度只是內(nèi)核的四分之一,代碼執(zhí)行也不會出現(xiàn)等待狀態(tài)。

然而,如果執(zhí)行轉(zhuǎn)移或跳轉(zhuǎn)指令,需要立即取出轉(zhuǎn)移或跳轉(zhuǎn)目標(biāo)地址的數(shù)據(jù),這樣,存儲器的等待狀態(tài)會增加系統(tǒng)開銷,這就是ART及其64項高速指令緩存發(fā)揮作用的地方。如果非順序指令第一次出現(xiàn),這條指令將從存儲器中取出并保存在64項高速緩存的一個存儲項內(nèi)。在下一次出現(xiàn)時,該指令將從高速緩存中直接取出,沒有等待狀態(tài)。

這個指令高速緩存還有一個LRU即最近不常用機制,因此,假如一個應(yīng)用軟件的轉(zhuǎn)移指令超過64條,最近常用的新指令將取代最近不常用的指令。這個架構(gòu)的優(yōu)點是,即便中斷服務(wù)處理程序被加速器覆蓋,這個機制仍然能夠支持各種轉(zhuǎn)移指令。

最常用的8行數(shù)據(jù)項目像高速指令緩存一樣,但是用于暫存最常用的數(shù)據(jù)庫,可以使D-bus總線立即充滿數(shù)據(jù)。

評論