中斷處理模式: 外部中斷處理和內部中斷處理的差異性

mtsr $r0, $IVB !write $IVB

INTC相關程序片斷:

INTC通常支持不同的中斷觸發方式,包含Interrupt Masking、Interrupt Trigger Mode、Interrupt Trigger Level …等。在開始使用每個中斷來源之前,這些控制選項都必須在INTC上設定正確。

3. 模擬結果

將上述的Reference Design整合完成后,搭配測試程序進行仿真,并藉由波形圖來觀察不同中斷模式下,相關中斷訊號線的變化。

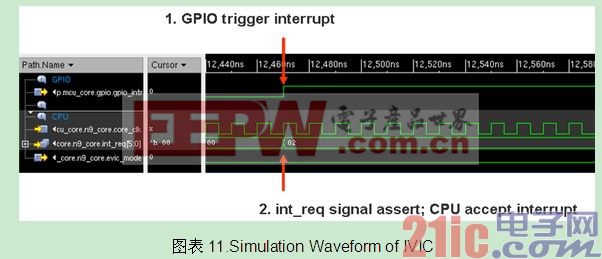

3.1 IVIC模擬結果

在IVIC仿真環境中,主要測試程序如下:

l 由GPIO觸發一中斷,并將中斷傳遞給CPU

l CPU接收到中斷后,執行相對應的中斷處理程序

仿真結果如圖表11所示,當GPIO觸發中斷后,將中斷直接傳遞給CPU,在CPU端的int_req訊號線會觸發,表示有中斷發生。當CPU收到中斷訊號后,接著會處理相對應的中斷處理程序。

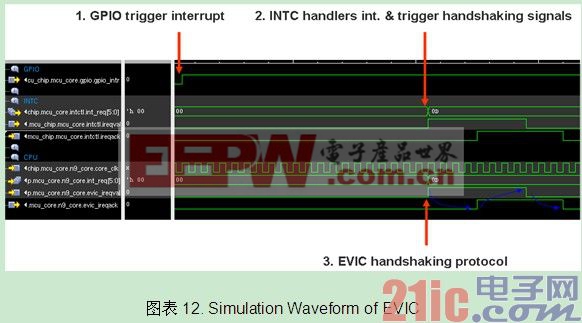

3.2 EVIC模擬結果

在EVIC仿真環境中,主要測試程序如下:

l 由GPIO觸發一中斷

l 此時INTC設D為EVIC模式,并將中斷訊號和相關溝通訊號傳遞給CPU

l CPU接收到中斷后,會將響應訊號拉起,告知INTC收到該中斷,并執行相對應的中斷處理程序

仿真結果如圖表12所示,當GPIO觸發中斷后,INTC將中斷和相關溝通訊號(ireqval)傳遞給CPU,在CPU端的int_req訊號線和evic_ireqval訊號線會觸發,表示有中斷發生。當CPU收到中斷訊號后,會將evic_ireqack訊號線拉起,告知INTC收到中斷。仿真結果如同章節1.2和圖表5所論述。

結語

在AndesCore™ N968A-S 所提供的兩種中斷模式里,其中的IVIC模式使用CPU內的中斷控制器來處理中斷,此模式對用戶來說,只要將中斷來源和CPU端的中斷訊號連接即可,相當容易整合。若用戶所設計的系統里,中斷來源數目超過IVIC模式所支持,或者系統需要更復雜的優先權選擇時,則可選用EVIC模式。在EVIC模式下,用戶需額外設計外部中斷控制器,并整合相關溝通訊號。因此,用戶可根據本身系統的復雜度和整合的難易度,來選擇適合的中斷處理模式。

水位傳感器相關文章:水位傳感器原理

評論