中斷處理模式: 外部中斷處理和內部中斷處理的差異性

在現今SOC設計中,當周邊裝置(Peripheral IP)想要和中央處理器(CPU)溝通時,最常使用的機制是透過中斷(Interrupt)。周邊裝置可觸發中斷給中央處理器,當中央處理器接收到中斷后,則可判斷是由那個周邊裝置觸發些中斷,接著處理相對應的中斷處理程序(ISR,Interrupt Service Routine),藉此達到彼此溝通的目的。

本文引用地址:http://www.104case.com/article/170443.htm而AndesCore™在中斷處理方面,共支持兩種模式:內部中斷處理器(IVIC Mode,Internal Vector Interrupt Controller)和外部中斷處理器(EVIC Mode,External Vector Interrupt Controller)。其中最大的差異性,即是中斷控制器所存在的位置。在內部中斷處理模式下,AndesCore™本身即設置了一個中斷控制器存在于CPU內部,經由此中斷控制器來處理相關中斷的工作。而在外部中斷處理模式下,用戶必須在CPU外部實做一個中斷控制器來處理相關中斷工作。

除了上述的差異性之外,在硬件方面的整合和軟件方面的應用,也存在些許差異性。本文之目的除了介紹這些差異性外,也提供一個簡單的設計平臺供使用者參考。期望能對使用者有所幫助,也希望讀者不吝指教提供您寶貴的意見。

1. 中斷處理模式介紹

AndesCore™共支持兩種中斷處理模式:內部中斷處理器(IVIC Mode,Internal Vector Interrupt Controller)和外部中斷處理器(EVIC Mode,External Vector Interrupt Controller)。以下的介紹將架構于AndesCore™ N968A-S這顆中央處理器。帶領使用者循序漸進地,了解這兩種中斷處理模式的差異。

1.1 Definition

AndesCore™ N968A-S支持兩種中斷處理模式,首先,我們先介紹關于這兩種模式的定義。

1.1.1 IVIC Mode

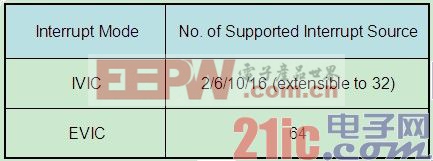

AndesCore™ N968A-S內部設計了一個中斷控制器,所支持的中斷來源數目可透過配置來決定。目前最大可支持16個中斷來源,但可擴充至32個。請參考圖表 1。若使用這存在于CPU內部的中斷控制器來處理相關中斷工作時,則為IVIC模式。假若SOC的中斷來源大于32個時,使用者還是可以使用IVIC模式,但是需要將多個中斷來源合為一個中斷訊號線(ex: OR function),且中斷處理程序(ISR)在該中斷訊號線觸發時,需要去判斷是由那個中斷來源所觸發。在N968A-S的IVIC mode之下,每個中斷來源可以選定值為0~3的優先權 (priority). 優先權高的中斷來源可以打斷優先權低的中斷來源。

1.1.2 EVIC Mode

假若IVIC模式不符合用戶所設計的系統,用戶就需要選用EVIC模式。在此模式下,用戶需要額外設計一個中斷控制器,用來處理周邊裝置和中央處理器之間相關中斷的工作,作為兩者間溝通的橋梁。

圖表 1. AndesCore™ N968A-S 所支持中斷來源數目

1.1.1 Interruption Vector Entry Points

為了加速中斷處理的時間,AndesCore™ N968A-S內部實做了一個Interruption Vector Table。將不同的中斷事件分別對應到不同的Vector Entry,當中斷發生時,CPU即可判斷中斷是由那個周邊裝置所觸發,并跳到該中斷所對應的Vector Entry,進而執行相關的中斷處理程序(ISR)。

在前面章節有介紹AndesCore™ N968A-S支持兩種不同的中斷處理模式。因此,在不同的中斷處理模式下,也對應了不同的Interruption Vector Table。

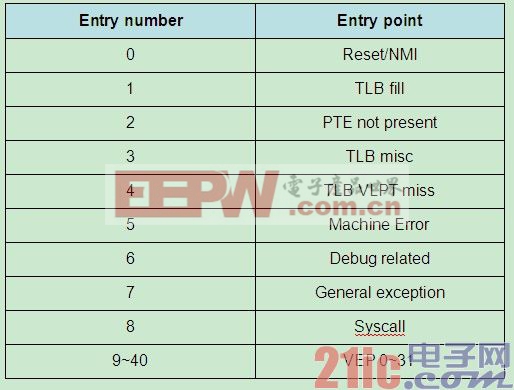

1.1.1.1 Interruption Vector Table of IVIC Mode

在IVIC模式下,所支持的中斷來源可由用戶來配置,支持的數目由2個到32個。Interruption Vector Table相關信息如下:

l 41 entry points (9 exceptions + 32 interrupts)

l Address = IVB.IVBASE + (entry number) * IVB.ESZ

(VEP: Vector Entry Point)

圖表2. Interruption Vector Table of IVIC Mode

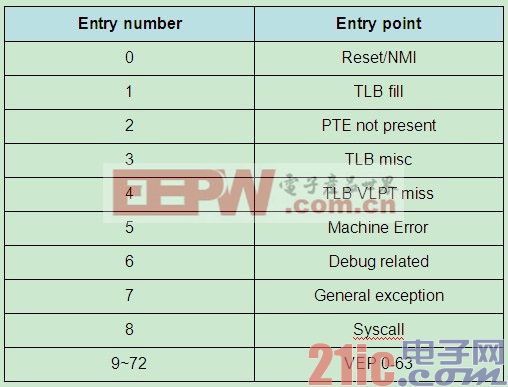

1.1.1.1 Interruption Vector Table of EVIC Mode

在EVIC模式下,所支持的中斷來源數目可達到64個中斷。Interruption Vector Table相關信息如下:

l 73 entry points (9 exceptions + 64 interrupts)

l Address = IVB.IVBASE + (entry number) * IVB.ESZ

圖表3. Interruption Vector Table of EVIC Mode

1.2 Signal Descriptions

AndesCore™ N968A-S 提供相關中斷訊號線,使得CPU可與周邊裝置或是外部中斷控制器溝通。在EVIC模式下,除了中斷來源訊號線之外,還包含了和外部中斷控制器相互溝通的訊號線,詳細訊號線敘述如下:

其中,evic_ireqval和evic_ireqack這兩個訊號線用來和外部中斷控制器溝通。在IVIC模式下,周邊裝置的中斷訊號可和int_req[N:0]直接整合。當周邊裝置觸發中斷時,相對應的int_req訊號會拉起,告知CPU該周邊裝置觸發了中斷,CPU即會跳到所對應的Vector Entry來執行相關的中斷處理程序。

而在EVIC模式下,外部中斷控制器會負責處理周邊裝置的中斷訊號。當周邊裝置觸發中斷時,外部中斷處理器會負責和周邊裝置溝通,并將相對應的中斷訊號(int_req)和中斷需求訊號(evic_ireqval)發給CPU,當CPU接收到中斷時,會將中斷接收訊號(evic_ireqack)拉起,告知外部中斷處理器收到中斷,并去處理相關中斷處理程序。

水位傳感器相關文章:水位傳感器原理

評論