手機功率放大器的功率包絡跟蹤

圖6顯示的是驗證VSG和AWG同步和重復性所使用的設置。 NI PXIe-5673E VSG用于生成RF波形,NI PXIe-5451用于生成基帶包絡波形。 NI PXIe-5154 1 GHz數字化儀用于同步驗證,但也可使用任何具有足夠高采樣率和帶寬的示波器。

本文引用地址:http://www.104case.com/article/170431.htm

為了同步AWG和VSG,兩個設備必須共享同一個10 MHz參考時鐘。 參考時鐘的來源可以是NI PXI 10 MHz背板時鐘,也可以是外部提供的10 MHz時鐘。

軟件

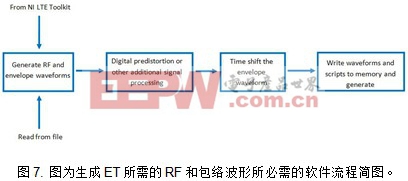

圖7顯示的是生成實現ET所需的RF和包絡波形所必需的軟件步驟。 要生成的LTE波形可使用NI LTE工具包來創建,或從文件中讀取。 然后便可計算包絡波形,包絡波形是LTE波形的一個函數。 您也許還希望進行一些額外的信號處理,比如數字預失真或其他濾波操作來優化用于ET的波形。 可對VSG進行配置來生成LTE波形,NI PXIe-5451的配置與NI PXIe-5673E VSG中的NI PXIe-5450 AWG相似(見圖5)。 接著包絡波形便可相對RF波形進行時移,并與用于控制波形生成的硬件腳本一起寫入到板載內存中。 (查看下面關于“波形生成延遲實現”的內容,了解包絡波形時移算法。) 最后,多個設備可通過TClk來進行同步和初始化。

同步基帶包絡發生器和RF信號發生器所需的軟件相對簡單。 VSG和AWG共享同一參考時鐘后,NI-TClk便可用于同步環節。 此時,對AWG和VSG生成的波形進行相位鎖定,兩個波形之間存在可重復延遲。 該延遲是由于NI-TClk沒有計算NI PXIe-5450 AWG到NI PXIe-5611 I/Q調制器之間的模擬路徑而產生的(詳見圖5)。 由于該延遲為常數,因此可通過設置AWG相對于VSG的延遲來進行消除。 對于許多ET應用,AWG相對于VSG的延遲(或VSG相對于AWG的延遲)對于找到延遲優化設備性能至關重要。 該延遲必須是可重復的,且具有最低程度的抖動,這是因為就算延遲只偏離最佳值幾納秒,也會使設備的線性度減少若干個dB。

波形生成延遲實現

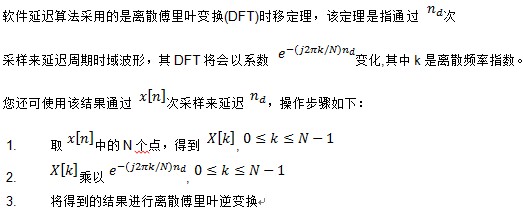

記住:VSG和AWG之間的延遲控制對于ET芯片測試和特性記述是至關重要的。 該延遲可通過在硬件中添加等待采樣和偏移采樣時鐘或通過在軟件中使用DSP來實現。 雖然在硬件中可實現該延遲,但是它需要ET波形重新采樣至200 MHz才能指定納秒級分辨率的延遲。 由于并非每個用戶都能夠對波形進行重新采樣,因此我們更傾向于在軟件中實現延遲。

電子管相關文章:電子管原理

三極管相關文章:三極管放大電路

pa相關文章:pa是什么

負離子發生器相關文章:負離子發生器原理 離子色譜儀相關文章:離子色譜儀原理

評論