基于cyclone EP1C6的LED大屏設(shè)計(jì)方案

3.3 FPGA控制單元軟件設(shè)計(jì)

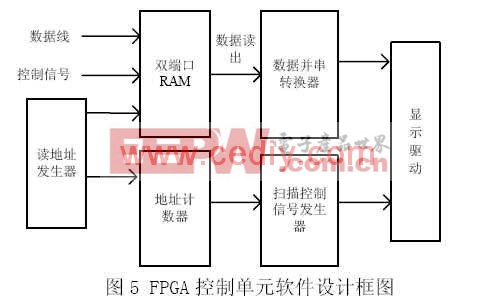

FPGA控制單元的設(shè)計(jì)是在QUARTUSII環(huán)境下完成,并用硬件描述語(yǔ)言VHDL描述,主要功能是配置雙口RAM、設(shè)計(jì)掃描控制電路。該單元的軟件設(shè)計(jì)模塊如圖5所示。

本文引用地址:http://www.104case.com/article/169530.htm

本文引用地址:http://www.104case.com/article/169530.htm雙端口RAM的配置完全通過(guò)在QUARTUS環(huán)境中設(shè)置菜單實(shí)現(xiàn),配置完成后將自動(dòng)生成一個(gè)VHDL文件,描述雙口RAM的內(nèi)部邏輯功能,雙口RAM在整個(gè)程序設(shè)計(jì)作為一個(gè)元件調(diào)用。

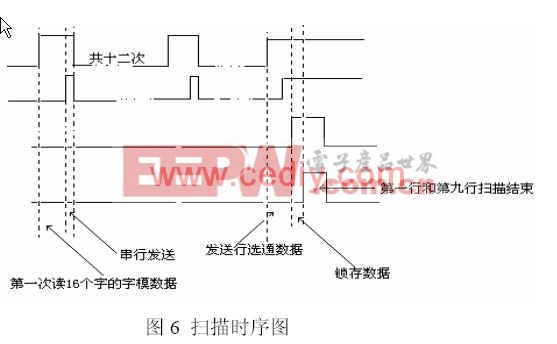

基于FPGA的掃描模塊的軟件設(shè)計(jì)如下:首先對(duì)FPGA總時(shí)鐘clk進(jìn)行64分頻得到clk1,clk1的低電平其間FPGA讀取雙口RAM的數(shù)據(jù),每4個(gè)clk周期讀一個(gè)16位的數(shù)據(jù),共讀出16個(gè)數(shù)。clk1的高電平期間FPGA進(jìn)行列掃描,每2個(gè)clk周期同時(shí)輸出16個(gè)數(shù)的1位,共32個(gè)周期將這16個(gè)數(shù)由并轉(zhuǎn)串輸出到16根數(shù)據(jù)線上,由于單片機(jī)寫(xiě)RAM的速度低于FPGA對(duì)數(shù)據(jù)的處理速度,剩下的32個(gè)clk周期用于等待單片機(jī)完成一個(gè)區(qū)的寫(xiě)操作。12個(gè)clk1周期后,一行的數(shù)據(jù)全部掃描完畢,F(xiàn)PGA輸出一個(gè)列鎖存信號(hào)給74LS595鎖存這些數(shù)據(jù),同時(shí)輸出行掃描信號(hào)和行鎖存信號(hào),接著掃描第二行,由于采用16根數(shù)據(jù)線進(jìn)行隔8行掃描,整個(gè)LED電子屏128行只要完成8次行掃描即可,時(shí)序如圖6所示。

5 結(jié)束語(yǔ)

通過(guò)采用自頂向下的設(shè)計(jì)思想,運(yùn)用EDA技術(shù)實(shí)現(xiàn)FPGA內(nèi)部雙口RAM的配置和掃描控制電路的設(shè)計(jì),將復(fù)雜的系統(tǒng)設(shè)計(jì)集成在一起,只需一片F(xiàn)PGA就可以實(shí)現(xiàn)所需的功能,高集成度帶來(lái)的不僅是成本降低,還提高了系統(tǒng)的穩(wěn)定性和可靠性。基于 cyclone EP1C6 的LED 大屏設(shè)計(jì)方案已成功應(yīng)用于我院的LED圖文發(fā)布電子屏,實(shí)踐證明:本系統(tǒng)能以多種播出方式顯示各種字體和型號(hào)的文字和圖形信息,與同類(lèi)設(shè)計(jì)相比,畫(huà)面清晰、性能穩(wěn)定、操作使用簡(jiǎn)單,具有很好的應(yīng)用前景。

評(píng)論