基于FPGA 的立體LED顯示驅動器的設計

系統硬件結構如圖1 所示。Nios Ⅱ主端口的時鐘是內部總線的時鐘,本系統采用50 MHz,用流模式傳輸的最大帶寬能達到100 Mbit/s。在電路設計時,首先用硬件描述語言寫用戶邏輯,創建Alvalon Slave 接口使之直接和DMA 控制器的主端口相連接, 完成硬件設計。再在Nios Ⅱ IDE 環境下,用C 語言編寫DMA 初始化和控制程序,使得流模式的數據傳輸在FIFO 與Avalon 總線的接口上,能夠做到無縫連接。

2.3 立體LED 控制器的設計:

Avalon 流模式LED 控制器硬件結構如圖2 所示,用硬件描述語言設計LED 時序發生器, 由于LED 各個像素點的色彩是以RGB 形式的亮度數據用二進制數字方式存儲在SDRAM 中的,使用D/T 轉換技術[5]即亮度時間轉換技術就可以實現LED 屏的全彩顯示。筆者設計了一個專用的函數f(i),用此函數即可統一控制各個像素點實現全屏幕所有像素點相互獨立而又同步的D/T 轉換。這里,f(i)作為LED_latch 信號。

圖2 Avalon 流模式LED 控制器結構圖

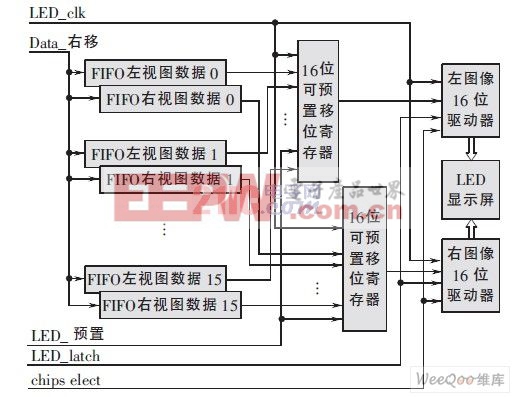

因為FIFO 中的數據格式是左、右視圖列交叉顯示,因此LED 控制驅動器的設計是以列驅動的。LED 時序發生器的設計如圖3 所示,將立體圖像對中左、右眼圖像幀每個像素的數據用乒乓開關控制存儲在FIFO 緩存之中,以16 個列像素點的驅動為例,FIFO 緩存之中的左、右視頻數據分別各連接一個16 位可預置移位寄存器,通過16 個時鐘脈沖的移位產生16 個像數的驅動數據,由片選信號選擇顯示行數,由D/T 轉換函數f(i)作為LED_latch信號鎖存,FIFO 緩存的數據經過8 次移位即可完成1 個像素的真彩驅動。

圖3 LED 時序發生器內部結構圖

每幀畫面顯示1 個立體像素真彩信號的時間需要移位8 次, 即250 個基本周期。如果LED 大屏幕顯示器每秒最多顯示30 幀, 采用1/8 驅動模式和立體像素的1/2時分復用, 再考慮選用16 位移位鎖存LED 恒流驅動電路,實際要求的時鐘頻率為2 MHz。

3 系統軟件設計與仿真:

軟件設計就是利用SoPC Builder 生成軟件文件,用文本編輯器編寫匯編語言或C/C++源程序,用GUNPro 將源程序編譯成可執行文件, 并通過下載電纜對可執行程序進行調試和運行。軟件系統分為兩部分:主程序和中斷服務程序。主程序主要完成系統的初始化,其主要功能是:對于系統中的每一個微處理器,從設備都生成一個定義該設備地址的頭文件,為軟件開發創建存儲器映射文件。DMA 的操作都通過中斷服務程序執行,把需要送出的像素信息排成一行順序送出形成數據流,借助于Avalon 流模式外設的設計方法, 實現一個Avalon 流模式的LED 控制器。利用DMA 控制器在流模式控制器和SRAM 之間建立一條DMA 傳送通道, 讓硬件來完成像素信息的自動讀取。軟件流程如圖4 所示,部分內部時序仿真如圖5 所示。

評論