基于FPGA的LED大屏幕控制系統(tǒng)設(shè)計(jì)

3 基于FPGA顯示屏控制器的設(shè)計(jì)

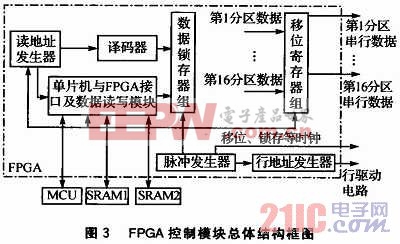

3.1 FPGA控制模塊總體方案

如圖3所示,FPGA控制模塊主要由單片機(jī)與FPGA接口及數(shù)據(jù)讀寫模塊、讀地址發(fā)生器、譯碼器、行地址發(fā)生器、數(shù)據(jù)鎖存器組、移位寄存器組、脈沖發(fā)生器等模塊組成。本文引用地址:http://www.104case.com/article/169049.htm

讀地址發(fā)生器主要產(chǎn)生讀地址信號(hào),地址信號(hào)送往MCU接口及數(shù)據(jù)讀寫模塊,讀取外部SRAM1或SRAM2中已處理好的LED顯示屏數(shù)據(jù),并把數(shù)據(jù)按分區(qū)方式送到數(shù)據(jù)鎖存器組鎖存。鎖存器輸出16分區(qū)數(shù)據(jù),通過移位寄存器組實(shí)現(xiàn)并串轉(zhuǎn)換得到顯示屏所需要的串行數(shù)據(jù),并送往LED顯示屏列驅(qū)動(dòng)電路。脈沖發(fā)生器為各模塊提供相應(yīng)的同步時(shí)鐘,行地址發(fā)生器產(chǎn)生相應(yīng)的行信號(hào)送往顯示屏的行驅(qū)動(dòng)電路。

3.2 單片機(jī)與FPGA接口及數(shù)據(jù)讀寫模塊

單片機(jī)與FPGA接口及數(shù)據(jù)讀寫模塊結(jié)構(gòu)如圖4所示。單片機(jī)從EEPROM中讀取數(shù)據(jù)并根據(jù)顯示要求進(jìn)行處理后,通過接口及數(shù)據(jù)讀寫模塊把數(shù)據(jù)送往數(shù)據(jù)緩沖器SRAM1或SRAM2。為提高數(shù)據(jù)的傳輸速度,保證顯示效果的連續(xù)性,在系統(tǒng)中采用雙體切換技術(shù)來完成數(shù)據(jù)存儲(chǔ)過程。也就是說,采用雙SRAM存儲(chǔ)結(jié)構(gòu),兩套完全獨(dú)立的讀、寫地址線和數(shù)據(jù)線輪流切換進(jìn)行讀寫。工作時(shí),F(xiàn)PGA在一個(gè)特定的時(shí)間只從兩塊SRAM中的一塊讀取顯示的數(shù)據(jù)進(jìn)行顯示,同時(shí)另外一塊SRAM與MCU進(jìn)行數(shù)據(jù)交換。MCU會(huì)寫入新的數(shù)據(jù),依次交替工作,可實(shí)現(xiàn)左移、上移、雙屏等顯示模式。如果顯示的內(nèi)容不改變,即一塊SRAM里的數(shù)據(jù)不變時(shí),MCU不需要給另外一塊SRAM寫數(shù)據(jù)。

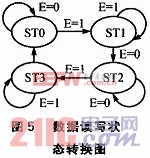

該模塊采用VHDL有限狀態(tài)機(jī)來實(shí)現(xiàn),整個(gè)控制分為4個(gè)狀態(tài),其狀態(tài)轉(zhuǎn)換圖如圖5所示。其工作過程如下:系統(tǒng)開機(jī)進(jìn)入初始狀態(tài)ST0,單片機(jī)的寫入使能端E為低電平,單片機(jī)從EEPROM中讀取數(shù)據(jù)并把數(shù)據(jù)寫入到SRAM1,同時(shí)FPGA讀取SRAM2中的數(shù)據(jù);當(dāng)單片機(jī)數(shù)據(jù)寫完一屏數(shù)據(jù)后E變?yōu)楦唠娖剑?dāng)FPGA從SRAM2中讀完數(shù)據(jù)、結(jié)束信號(hào)READ_END為低電平時(shí),進(jìn)入ST1狀態(tài)。

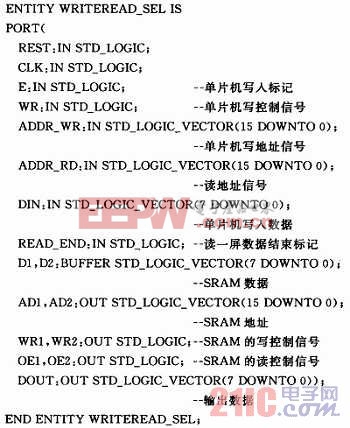

在ST1狀態(tài)下,若沒有新的數(shù)據(jù)寫入則E保持高電平,F(xiàn)PGA讀取SRAM1的數(shù)據(jù),為靜態(tài)顯示;只有當(dāng)單片機(jī)的讀入控制信號(hào)E為低電平且READ_END為低電平時(shí),進(jìn)入ST2狀態(tài)。在ST2狀態(tài)下,單片機(jī)把數(shù)據(jù)寫入SRAM2,同時(shí)FPGA讀取SRAM1的數(shù)據(jù),單片機(jī)數(shù)據(jù)寫完后E變?yōu)楦唠娖剑?dāng)FPGA一屏數(shù)據(jù)讀完后READ_END為低電平,進(jìn)入ST3狀態(tài)。在ST3狀態(tài)下,如果沒有新數(shù)據(jù)寫入E為高電平,F(xiàn)PGA讀取SRAM2中的數(shù)據(jù)。當(dāng)單片機(jī)有新的數(shù)據(jù)寫入時(shí)E變?yōu)榈碗娖剑?dāng)FPGA一屏數(shù)據(jù)讀完后READ_END為低電平時(shí),重新進(jìn)入ST0狀態(tài)。通過這種周而復(fù)始的交替工作完成數(shù)據(jù)的寫入與讀取,其端口程序如下:

評(píng)論