基于CDMA的無線網絡視頻監控系統的設計

由于攝像頭輸出模擬信號,需要經過視頻A/D轉化后,把模擬視頻信號轉化成數字視頻信號,輸入進FPGA芯片,FPGA根據狀態信號SRTS0把奇偶場圖像信號分別存儲在SDRAM(ODD)和SDRAM(EVEN)中。

3.2 圖像處理模塊

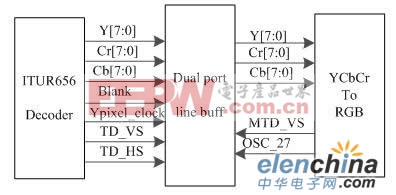

由圖3可以清楚的看出圖像處理過程,攝像頭采集信號經A/D轉換后送入ITU R656解碼器(Decoder),經解碼后分出的Y、Cr、Cb三種基色信號數據線,這三種基色信號、控制信號和時鐘信號進入緩沖器(Buffer)后共同作用輸出Y[7:0]、Cr[7:0]、Cb[7:0]三種基色信號線給RGB模塊,通過對三種基色的混合調制便可得到彩色的圖像畫面。

圖像傳輸過程中需要對圖像信息進行壓縮。由于通常無損壓縮的壓縮比不高,所以在很多情況下,經過無損壓縮后的數據量仍將超過實際應用所能忍受的負荷。所以實現有較高壓縮比的高保真的有損圖像壓縮就很重要。

圖3 圖像處理模塊

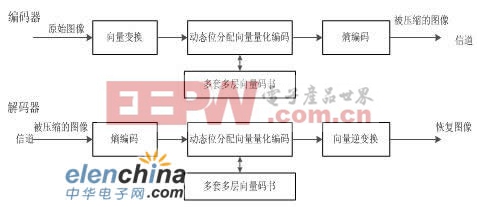

本算法的編碼器包括3個步驟:第1步是對原始圖像進行向量變換,第2步是動態位分配的向量量化VQ(Vector Quantization)編碼,第3步是進行一種熵編碼。相應的解碼器也包括3個步驟:解碼器由編碼器的3個步驟的逆過程按逆序組成。圖4所示為算法編碼器和解碼器的框架圖。

圖4 編碼器和解碼器的框架

圖像處理部分是整個系統的核心,需要對外圍的器件進行集中控制和處理。FPGA/CPLD對圖像信號的采集、控制、存儲數據到SRAM以及從SRAM讀取數據都在這里實現。選用CycloneII EP2C20F484C7芯片,利用Verilog HDL作為硬件描述語言,實現對各小模塊的連接控制。

3.3 VGA顯示模塊

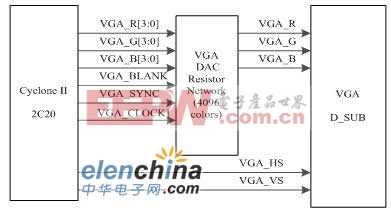

如圖5 VGA顯示模塊所示,從攝像頭過來的信號經過視頻解碼后到視頻處理芯片,視頻處理芯片輸出三路的R、G、B數字信號到視頻DAC,然后輸出三路的模擬R、G、B信號到顯示屏顯示。.這其中,視頻DAC的速度直接決定了輸出圖像的分辨率和刷新率,而其精度則決定了輸出圖像的質量。DAC的速度和分辨率的關系可以通過下面的關系式得到:

時鐘頻率=點速率=(水平分辨率)×(垂直分辨率)×(刷新率)/(回掃系數);

水平分辨率=行的像素數目;

垂直分辨率=幀的像素數目。

圖5 VGA顯示模塊

CDMA(Code-Division Multiple Access)技術是近年來在數字移動通信進程中出現的一種先進的無線擴頻通信技術,具有頻譜利用率高、話音質量好、保密性強、掉話率低、電磁輻射小、容量大、覆蓋廣等特點。

1)數據傳輸方式設計

評論