數字網絡視頻監控器中多路轉接邏輯的設計

如圖1所示,A/D芯片接受來自四個攝像頭的四路模擬視頻信號,這里采用Techwell公司的TW2804芯片,此芯片支持四路視頻模擬信號的輸入,輸出是數字ITU-R BT.656格式的信號,時鐘是27MHz。D1、D2、D3、D4信號的時序圖如圖2所示。

圖2 ITU-R BT.656格式信號時序圖

其中EAV和SAV分別為行尾和行頭標志信號,他們中間是行與行之間的空白信號,SAV后面的VALID有效時的信號為1440bytes的d1格式的有效視頻信號,總的這些信號加起來是視頻信號的一行信號,一幀視頻信號包括576行這樣的行信號,也就是有效的這種格式的一幀輸出視頻信號為1440*576bytes的信號,由于每一行信號中由兩個bytes來表示一個像素,所以這種d1格式一幀的像素為720*576分辨率。

FPGA轉接邏輯要實現的功能是要在顯示終端上同時顯示四路的視頻信號。也就是要顯示如圖3所示的視頻信號。

由于要在一個顯示終端上同時顯示四路信號,所以原來每一路信號的720*576分辨率要轉換為原來1/4的分辨率,即cif的格式,cif格式是352*288的分辨率,這樣四路cif格式的信號組合成如圖3所示的一個幀輸出到終端顯示出來。

因為在終端顯示上是要求四路視頻信號同步輸出的,也就是不允許出現其中一路信號已經在顯示器上顯示出來了,但另外一路信號還沒有顯示出來,也就是出現畫面上一部分是黑屏的情況,所以在這種情況下,需要把四路不同的視頻信號先用FPGA在SDRAM中緩存起來,當每一路信號都在SDRAM中都至少存滿一幀時就可以同步讀出,并通過FPGA內部緩存組成如圖3所示的幀格式,然后輸出給壓縮芯片壓縮后由處理器控制輸出至網絡,這里的壓縮芯片選的是VWEB公司的VW2010。

圖3 顯示終端視頻信號格式

至此,FPGA要實現的功能已經非常清晰,首先把輸入的四路d1格式的信號分別轉換成四路cif格式的信號,然后把這四路信號分別緩存在SDRAM中,當SDRAM中每一路信號都至少存滿一幀時,同步讀出,讀出SDRAM到FPGA中后,經過格式的重新組合,最后組成如圖3所示的信號格式輸出。其中數據在SDRAM中的緩存控制是最重要也是最復雜的環節。下面詳細介紹此FPGA的邏輯設計與實現。

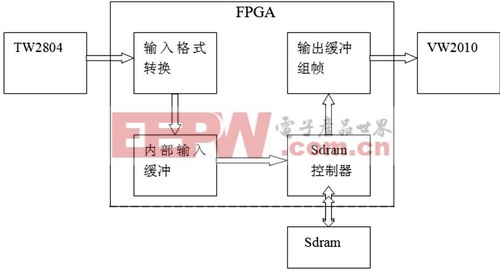

由上面的介紹可知,此FPGA主要有三方面的接口,與TW2804的輸入接口,與SDRAM的緩存接口,與VW2010的輸出接口。所以FPGA的內部邏輯大致可以設計為如圖4所示。

圖4 FPGA內部邏輯結構框圖

評論