高清晰度數字電視傳輸系統設計與實現

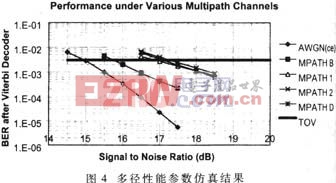

DMB-T系統中是在時域插入序列,利用信道的沖擊響應來進行信道估計,對數據傳輸率的影響為7%。高斯噪聲和時變信道對本信道估計算法的影響并不大,而且由于在開發設計過程中對算法進行了較多的優化與改進,所以本系統在抗多徑干擾方面具有突出的性能,對移動接收環境尤其適用。對系統參數的仿真結果如圖4所示。

3 系統同步性能仿真

為了評估系統的同步性能,設計了專門的同步電路,包括transmitter、Code acquisition、STR、AFC、FFT和Channel Estimation等部分,完整地實現了系統同步功能。仿真的交互式界面如圖5所示。

圖5中的Time ms 域示出的是實際系統運行的時間與仿真時間不同,下面各域表示頻率偏移、時間偏移以及設計系統同步電路估計出來的頻偏和時偏,在捕獲同步序列后Code Acquisition Lock″域由紅變綠,右半部分的域表示了信道估計之前和之后對應的星座圖。從仿真可以得到整個碼同步捕獲時間僅僅需要5ms 這比同類系統的同步時間大大縮短,且時偏和頻偏的糾正都達到了設計要求。

在DMB-T中同時利用了時域和頻域的信息進。

采樣時鐘同步,利用擴頻偽隨機PN序列進行載波同步,信號的捕獲時間縮短為5ms,并在20ms以內就能夠完成時域和頻域糾正,系統實現同步。

4 設計實現的流程

以往的設計流程中沒有系統級仿真這一步,通常是在硬件完成以后才能進行修改和優化,而在系統級這個層次上進行的算法優化和參數調整不僅成本低,而且效率也很高。通過不斷調整系統參數和改進相關算法得到最優性能和理論上的最優參數。從前面可以看出,采用SPW軟件進行系統級設計與仿真可以讓設計者把主要的精力放在系統的算法實現及優化上,而不必過多地考慮具體硬件實現。

當這些系統級仿真都全部完成以后,如圖1的流程圖所示,采用Cadence公司的硬件設計系統HDS、Verilog仿真軟件Verilog-XL和NC-Verilog、SPW和Verilog協同仿真軟件等把SPW中的系統級設計轉換為RTL級的Verilog硬件描述語言,用FPGA實現、PCB布板進行驗證。對FPGA實現的原型樣機進行實地測試以后,可以把完整的設計做成專用集成電路ASIC。

評論