C2H技術在視頻監控系統中的應用

各模塊功能描述如下:NiosII 軟核CPU 是32 位的RISC 嵌入式處理器,為整個系統的中樞;SDRAM,是系統大容量的數據緩沖存儲區域;Flash,存儲系統的硬件和軟件的系統上電配置數據;視頻處理模塊,實現對視頻流的ITU656 解碼、去隔行、格式轉換等功能。

2.2 C2H 在視頻監控系統的應用

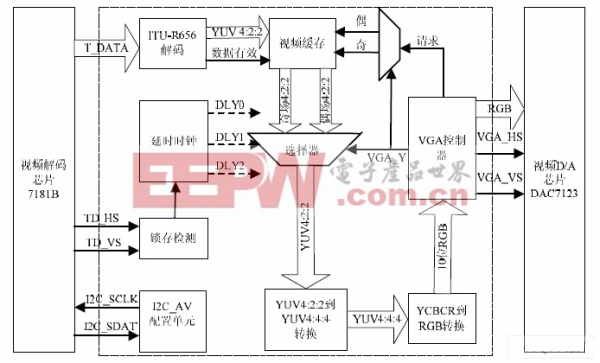

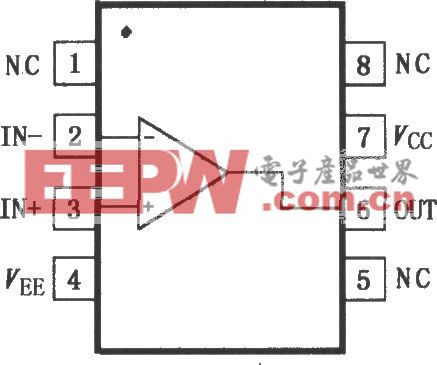

下圖 1.2 詳細表示出了系統中視頻數據流的處理過程。

圖2 視頻數據流處理過程圖

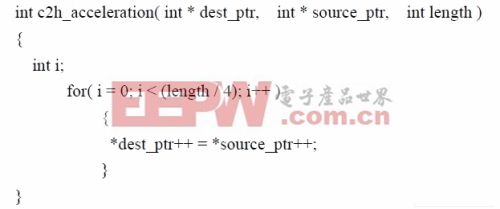

從上圖 2 可以看出,數據流處理過程是先經過視頻解碼芯片AD7181B 的模數轉換,變成8 位的數字視頻信號;再由ITU-R656 解碼器解碼,使視頻格式變成YUV4:2:2;然后對視頻流進行去隔行處理。去隔行處理中,需要將奇場數據和偶場數據分別存于兩個FIFO(FIFO A 和FIFO B)中,然后再以兩倍的頻率按ABABA……的順序讀出,便可完成視頻的去隔行處理。最后經過YUV 到RGB 時域變換,便可在VGA 控制器的控制下在顯示器上進行顯示。由于視頻解碼A/D 和視頻D/A 是由專用的芯片完成,速度很快,未對系統的速度有太大影響。經過分析比較,系統性能提升的瓶頸是數據中間處理中的數據讀寫等環節。由于涉及到從存儲器讀數和寫數,使這部分成為系統中最耗時的部分。所以提高系統性能的關鍵是從減少數據讀寫的時間耗費入手。本設計中針對這一點,采用C2H 技術,對數據的讀寫進行硬件加速。進行加速部分程序如下:

其中,dest_ptr 是數據目的地址,source_ptr 是數據原地址,length 是字節數,測試中length取1048576 個字節長。

實現過程按照論文 1.2 節所述。首先,經過對時耗的分析比較,確定耗時最多的部分是數據讀寫部分。因此,確定這個環節為加速對象,并將其編寫為獨立的子函數,即上述的 c2h_acceleraTIon 函數,然后在IDE 中直接選擇以上函數,點擊右鍵,選擇HardwareAcceleration,最后再重新生成系統并編譯整個工程。

評論