基于超薄外延技術的雙擴散新型D-RESURF LDMOS設計

2 器件的仿真優化設計

設計中應用MEDICI、Tsuprem4軟件對器件進行優化。在符合4.5μm薄外延的工藝條件下,為改善器件表面電場,使器件最高耐壓大于700V的設計要求,對P-top注入劑量與結構尺寸進行了仿真優化設計。同時,分析了漂移區濃度對擊穿電壓和導通電阻的影響,通過仿真得出最佳濃度分布范圍。

2.1 P-top注入劑量與結構尺寸的仿真優化

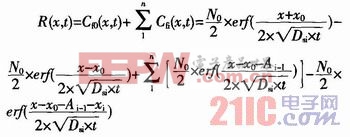

由于在縱向P-top降場層的結深都很淺,所以其濃度變化可以忽略不計。在這里主要分析P-top降場層沿x方向的一維模型,多環注入時雜質濃度分布為R(x,t),Cfo(x,t)和Cfi(x,t)分別是當推結時間(T)后的第一個環和第i個環的雜質濃度分布,其公式為:

通過公式可以調節在版圖中P-top環的窗口尺寸和間距的大小,實現P-top降場層的線性變摻雜。考慮工藝制作水平和誤差等因素,為避免出現工藝失真,窗口的尺寸和間距不易太小,但如果窗口的間距太大,就不易實現降場層的線性變摻雜,因此需選取合適的窗口尺寸和間距。經過仿真設計與實際測試,得到兩組具體的窗口尺寸,見表1。本文引用地址:http://www.104case.com/article/166181.htm

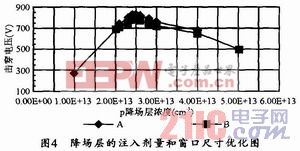

對P-top降場層的注入劑量和窗口尺寸進行優化設計,其模擬結果如圖4所示,由圖可見窗口尺寸較小時(A結構)更近似為線性變摻雜,其濃度在2.2E13cm-3~3E13cm-3范圍內都滿足器件擊穿電壓大于700V,而窗口尺寸較大的B結構注入劑量只在2.3E13cm-3~2.8E13cm-3范圍內才滿足器件擊穿電壓大于700V,顯然其變化范圍較小,提高了工藝的復雜程度,所以這里選取A結構中最優值2.5E13cm-3進行工藝設計。

評論