第四代無線基礎(chǔ)架構(gòu)的離散式 SerDes 解決方案

對(duì)于八天線波束形成LTE系統(tǒng)而言,式3中的SDR會(huì)倍增為9.8Gbps。因此,I-Q取樣寬度、信道寬度或天線載波數(shù)目的增加會(huì)直接造成REC與RE之間序列數(shù)據(jù)速率的提高。搭建基礎(chǔ)架構(gòu)的網(wǎng)絡(luò)設(shè)備制造商應(yīng)該要了解,在LTE演進(jìn)中,序列數(shù)據(jù)速率必須從614.4Mbps的中等速率調(diào)整為9.8Gbps或12.2Gbps。DBSA的高SDR需要光纖纜線兩端的SerDes發(fā)揮更高的效能,才能達(dá)到穩(wěn)定的頻率數(shù)據(jù)復(fù)原,并符合CPRI或OBSAI標(biāo)準(zhǔn)的抖動(dòng)規(guī)格。為了進(jìn)一步了解4G的SerDes及數(shù)據(jù)處理效用,以下將分析CPRI/OBSAI的通信協(xié)議堆棧。

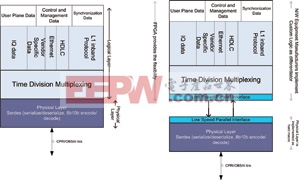

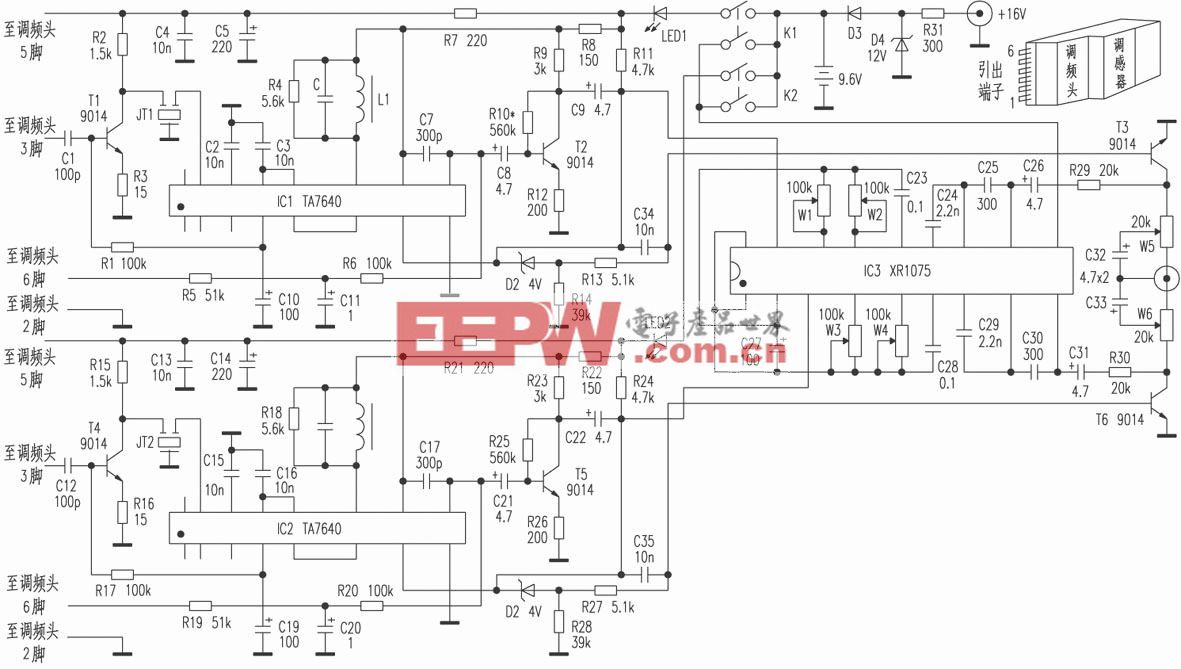

圖3a顯示CPRI通信協(xié)議層堆棧。一般而言,物理層包含不同通信協(xié)議都具備的固定功能。CPRI/OBSAI通信協(xié)議層的固定功能物理層是以硬件宏(hard marco)的方式進(jìn)行實(shí)作,以達(dá)到嚴(yán)格的時(shí)序閉合需求。然而,邏輯層則允許客制化。由于新興的標(biāo)準(zhǔn)演進(jìn),以及網(wǎng)絡(luò)設(shè)備制造商期望透過專屬功能建立附加價(jià)值,使得邏輯層會(huì)隨之更新。在實(shí)作CPRI/OBSAI接口的邏輯層部份時(shí),F(xiàn)PGA通常會(huì)提供所需的彈性。FPGA的邏輯項(xiàng)目能夠利用程序加以設(shè)計(jì),以支持自定義的邏輯層。

圖3a CPRI通信協(xié)議層堆棧

圖3b CPRI通信協(xié)議層堆棧(外部SerDes劃分)

由于網(wǎng)絡(luò)設(shè)備制造商改采4G部署,因此不僅需要相同彈性來實(shí)行邏輯層,也需要強(qiáng)化SerDes效能來滿足增加的 SDR。網(wǎng)絡(luò)設(shè)備制造商可選擇采購已整合SerDes的FPGA,或選擇采購FPGA與離散式SerDes,然后將兩者結(jié)合(見圖3b)。

以下是選擇離散式SerDes-FPGA及整合型SerDes-FPGA時(shí)必須考慮的幾項(xiàng)關(guān)鍵因素:

● 離散式SerDes加上FPGA的成本VS已整合SerDes的FPGA成本

● 離散式SerDes的效能VS整合于FPGA的SerDes效能

● 對(duì)于特定FPGA平臺(tái)的熟悉程度

● 改用整合型SerDes-FPGA所節(jié)省的空間

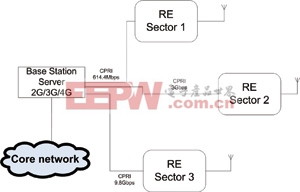

圖4顯示2G/3G/4G基站或REC連接到分別服務(wù)3個(gè)區(qū)塊的3個(gè)RE。其中,3個(gè)CPRI設(shè)定分別為614.4Mbps、3Gbps及9.8Gbps線路速率,并假設(shè)9.8Gbps為更新過后的SDR,可支持4G。

圖4 連接到3個(gè)RE的2G/3G/4G REC

狀況A:假設(shè)網(wǎng)絡(luò)設(shè)備制造商使用FPGA與離散式SerDes,而且已經(jīng)在該特定FPGA平臺(tái)的學(xué)習(xí)周期中投入時(shí)間與資源。若要在此狀況下支持9.8Gbps:

● 制造商將SerDes升級(jí),并持續(xù)使用同一個(gè)熟悉的FPGA平臺(tái)。優(yōu)點(diǎn):達(dá)到規(guī)模效益,因?yàn)閳D4顯示的3個(gè)RE區(qū)塊都能具備類似的FPGA,同時(shí)以不同的SDR進(jìn)行運(yùn)作。如此一來,制造商便不需要變更FPGA平臺(tái)而經(jīng)歷學(xué)習(xí)周期。

狀況B:網(wǎng)絡(luò)設(shè)備制造商使用已整合SerDes功能的經(jīng)濟(jì)型低階FPGA。若要在此狀況下支持9.8Gbps,制造商有3種選擇:

● 改用不同制造商的9.8Gbps高階FPGA(已整合SerDes)。缺點(diǎn):成本增加,而且制造商必須經(jīng)歷新FPGA平臺(tái)的學(xué)習(xí)周期。

● 改用相同制造商的低價(jià)9.8Gbps FPGA(已整合SerDes)。缺點(diǎn):效能疑慮。

● 向同一個(gè)廠商購買不含SerDes的FPGA,并將系統(tǒng)切割為FPGA以及離散式SerDes。優(yōu)點(diǎn):制造商改用不含SerDes的FPGA可以節(jié)省成本,同時(shí)保留熟悉的FPGA平臺(tái)。此外,使用相同的FPGA可切割出采用離散式SerDes的3個(gè)RE區(qū)塊,進(jìn)而達(dá)到規(guī)模效益,就如圖4所示。缺點(diǎn):離散式SerDes加FPGA的解決方案可能需要更多的PCB空間。

狀況C:網(wǎng)絡(luò)設(shè)備制造商使用已整合SerDes的高階FPGA。若要在此狀況下支持9.8Gbps,制造商有3種選擇:

● 改用相同制造商的9.8Gbps FPGA(已整合SerDes)。缺點(diǎn):制造商可能必須為具備9.8Gbps SerDes功能的FPGA付出相當(dāng)高的成本。

● 改用不同制造商的9.8Gbps低階FPGA(已整合SerDes)。缺點(diǎn):學(xué)習(xí)周期、效能疑慮、缺乏降低成本的規(guī)模效益。

● 向同一個(gè)廠商購買不含SerDes的FPGA,并將系統(tǒng)切割為FPGA及離散式SerDes。優(yōu)點(diǎn):與狀況B類似。

在9.8Gbps或12Gbps等高SDR的情況下,要滿足離散式SerDes設(shè)計(jì)中對(duì)于穩(wěn)定頻率數(shù)據(jù)復(fù)原、抖動(dòng)容差、信號(hào)調(diào)節(jié)及信號(hào)完整性的需求已經(jīng)相當(dāng)不容易,更不用說在整合型SerDes-FPGA設(shè)計(jì)中,數(shù)字邏輯項(xiàng)目區(qū)塊(芯片的大部份)內(nèi)敏感模擬電路的噪聲隔離會(huì)造成設(shè)計(jì)上更大的挑戰(zhàn)。有時(shí)候,為達(dá)到所需的效能,已整合SerDes的FPGA需要高成本的電源供應(yīng)濾波,并選擇使用電壓控制的晶體振蕩器或成本較低的晶體振蕩器。這些需求會(huì)增加實(shí)施的成本。概括來說,將SerDes整合于FPGA會(huì)造成相關(guān)的成本,而且當(dāng)整合難度因?yàn)镾DR升高而增加時(shí),這些成本也會(huì)增加。這正是為何當(dāng)數(shù)據(jù)速率在3Gbps或更低的狀況下,F(xiàn)PGA加離散式SerDes的解決方案比整合型解決方案更符合成本效益的一個(gè)主要原因。

結(jié)論

當(dāng)網(wǎng)絡(luò)設(shè)備制造商建置4G的基礎(chǔ)架構(gòu)時(shí),對(duì)于分布式基站架構(gòu)部署中無線電設(shè)備控制及無線電設(shè)備之間的高序列數(shù)據(jù)速率需求將大幅升高。要滿足如此需求,光纖纜線兩端的SerDeson必須發(fā)揮更高的效能。網(wǎng)絡(luò)設(shè)備制造商可將系統(tǒng)切割開來,便能使用同一個(gè)熟悉的FPGA平臺(tái)進(jìn)行邏輯層處理。為達(dá)到高序列數(shù)據(jù)速率,網(wǎng)絡(luò)設(shè)備制造商可改用離散式 SerDes 解決方案,單獨(dú)就SerDes部份進(jìn)行升級(jí)。如此的切分可達(dá)到所需的效能而不必采用新FPGA平臺(tái)所需的學(xué)習(xí)周期,并且有助于提升規(guī)模效益,最終能降低制造商的成本。

評(píng)論