基于CX2443x的數字電視機頂盒設計

1 音視頻信號解碼處理的流程

數字電視技術的首要目標是提高傳送圖像的質量,完成對數字有線電視的相關改造后,不僅傳送圖像的質量而且傳送圖像的數量均要得到提高。CX2443x是高度集成的單片IC,它在一塊芯片上包含了完整的STB后端子系統和CM子系統。其后端子系統包含有一個視頻解碼器、一個音頻解碼器、三個多標準傳輸流解復用器和高性能的嵌入式32位ARM920T RISC處理器以及集成的外設I/O接口等。CX2443x片上的數字電視解碼內核能夠對音視頻流信號進行完全的解碼并最終輸出數字的視頻和音頻信號到編碼模塊。

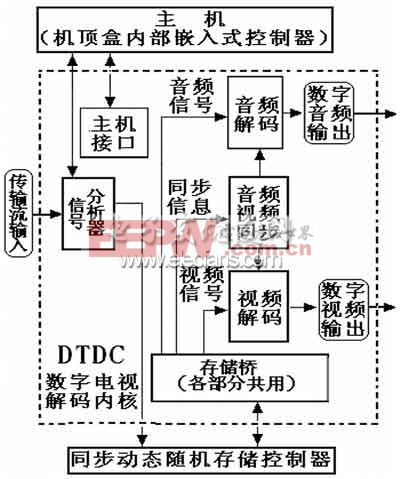

信號流的處理過程如圖4所示。完成了解調和信道解碼的MPEGⅡ格式或其他格式的音視頻信號傳輸流在解復用模塊進入DTDC子系統,它包含了音視頻的基本碼流、同步信息、程序導航和解密信息。解復用分析器標識這些不同格式的數據并輸送每一格式的數據到相應的內存緩沖器。程序導航和解密信息則被輸送到DTDC外部主機;音視頻的基本碼流被輸送到專用的SDRAM中,并通過存儲橋傳送到相應的解碼器以輸出音視頻的解碼數字信號;同步信息則被輸送到一個音視頻同步機。

圖4 數字電視數字解碼子系統結構圖

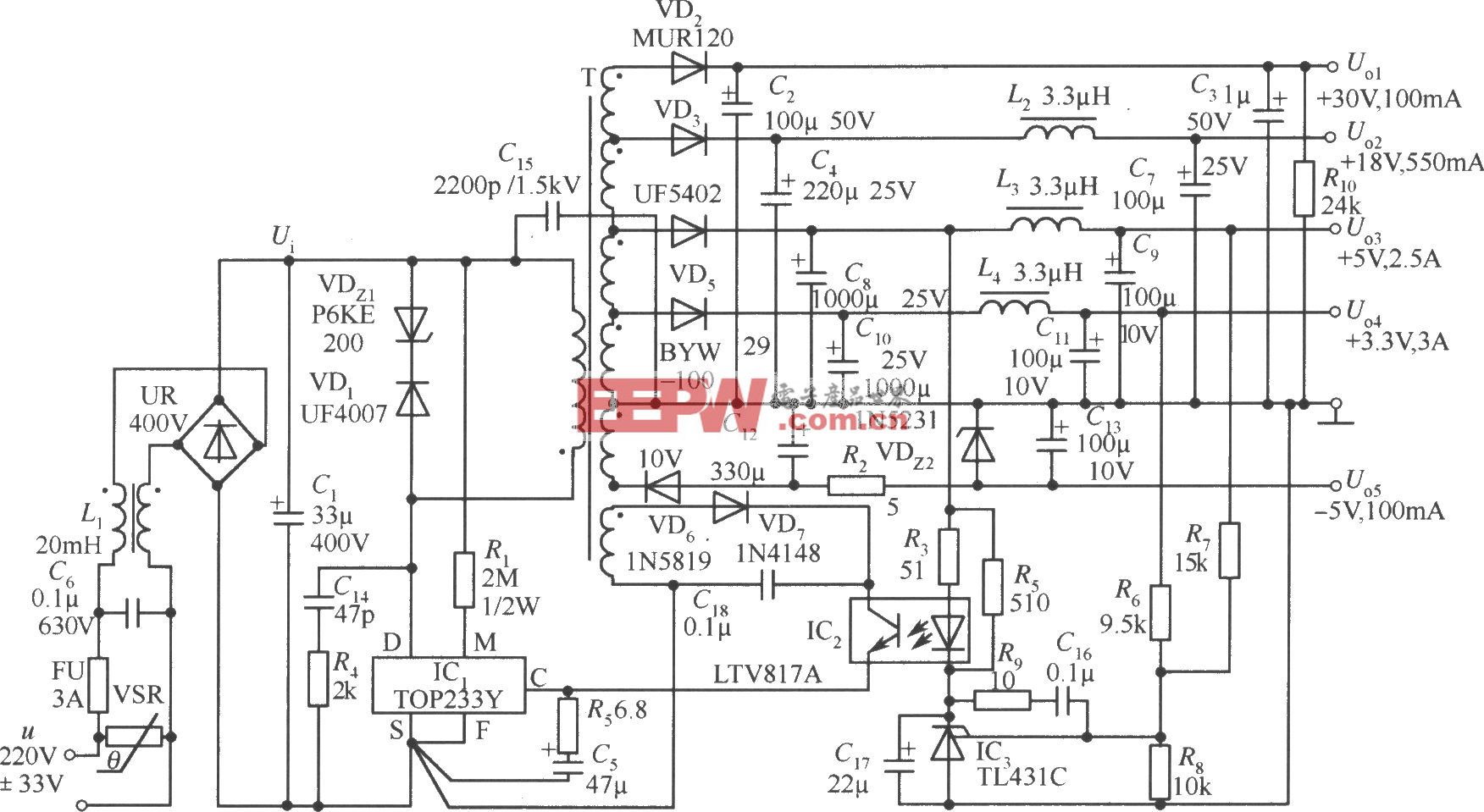

2 音視頻解碼模塊的電路設計實現

CX2443x和其他子芯片以及晶振電路協同完成信號的解碼處理,如圖5所示,這部分設計主要包含音頻視頻信號模塊、系統調試用的JTAG口的電路連接,以及一些外圍電路。CX2443x芯片輸出完成數字解碼的音頻和視頻到相應的編碼模塊。JTAG口用來連接外部的調試設備,在實際電路設計中要注意外部晶振電路的配合。

圖5 音視頻解碼模塊的電路

機頂盒音視頻解碼測試

經過初步的測試,本樣機設計符合以下標準:信道解碼遵循DVB-C EN300 429;視頻解碼遵循MPEG-2 Video(MP@ML)和MPEG-1 Video;音頻解碼遵循MPEG-2、MPEG-1和線性PCM。數字電視信號解碼處理后的圖像如圖6所示。

圖6 解碼圖像的顯示

評論