視頻信號數(shù)字化光纖傳輸實驗裝置的研制

2)隨機同步方式 該組芯片在沒有同步信號傳輸的情況下仍然可以完成鎖定,這使該組芯片在開放場合得到應(yīng)用。隨機同步時,串化器不發(fā)送同步信號,解串器直接對差分數(shù)據(jù)流進行鎖定,該鎖定方式會受到初始時數(shù)據(jù)和時鐘的相位影響,也會受到數(shù)據(jù)本身的影響,當(dāng)一個特殊的數(shù)據(jù)圖樣反復(fù)出現(xiàn)時,解串器可能出現(xiàn)鎖定錯誤,稱為RMT。但當(dāng)同步丟失后,解串器會重新鎖定時鐘,恢復(fù)同步。

由于該電路采用隨機同步方式。串化器的SYNC1和SYNC2懸空。

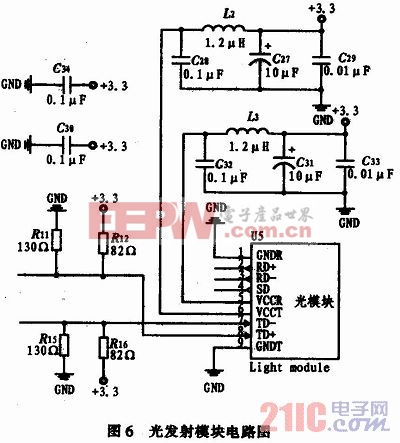

2. 4. 2 電/光模塊

采用型號為HNMS-XEMC41XSC20,工作波長在T1310nm/R1550nm的單纖雙向一體化收發(fā)模塊,將電信號差分數(shù)據(jù)流轉(zhuǎn)成光數(shù)據(jù)信號流,電路如圖6所示。本文引用地址:http://www.104case.com/article/165897.htm

2.5 信號的接收及處理

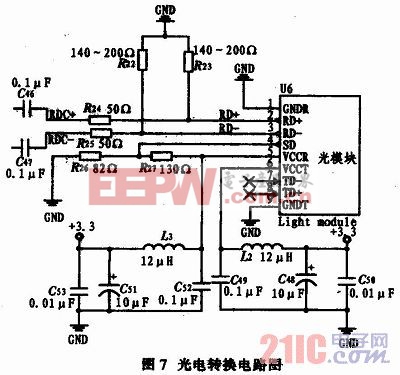

2.5.1 光/電轉(zhuǎn)換模塊

裝置以單纖進行信號傳輸,光信號傳輸到接收裝置后,需要還原為電信號,即差分電壓數(shù)據(jù)流。采用型號為HNMS-XEMC41XSC20,工作波長在T1310 nm/R1550 nm的單纖雙向一體化收發(fā)模塊,將光信號轉(zhuǎn)換為電信號。轉(zhuǎn)換后的差分信號由RD+和RD-輸出。電路如圖7所示。

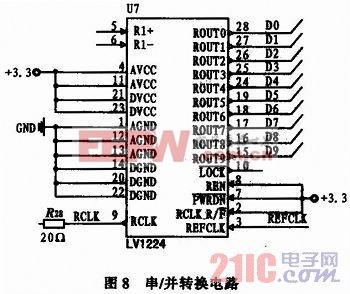

2. 5. 2 串并轉(zhuǎn)換

裝置采用與發(fā)送器中的串化器DS92LV1023相匹配的解串器DS92LV1224。發(fā)送器中的串化器將10位的并行數(shù)據(jù)轉(zhuǎn)換為串行的差分數(shù)據(jù)流,因此在接收器中需用相應(yīng)的解串器將串行差分數(shù)據(jù)流還原為并行數(shù)據(jù)。

DS92LV1224內(nèi)部有鎖相環(huán),在接收數(shù)據(jù)流時可以根據(jù)數(shù)據(jù)的頻率自行匹配接收時鐘,外界只需為其提供參考時鐘。此處參考時鐘選為16MHz,由FPGA控制部分提供。芯片還匹配了與解串后的數(shù)據(jù)同步的時鐘,以助于轉(zhuǎn)換后的并行數(shù)據(jù)輸出。參考時鐘和數(shù)據(jù)輸出時鐘分別為REFCLK和RCLK引腳。為了保證視頻信號的連續(xù)性和實時性,需避免芯片處于省電模式或高阻模式。因此PWRDN和REN需接高電平。RCLK-R/F接高電平,即選擇時鐘上升沿輸出數(shù)據(jù)。

該組芯片有2種同步方式:快速同步和隨機同步。快速同步是由串化器發(fā)送一組由連續(xù)的6個“1”和“0”組成的同步信號,解串器收到信號后鎖定數(shù)據(jù)時鐘,鎖定完成之前LOCK保持高電平,同步完成后跳變?yōu)榈碗娖健M叫盘柕陌l(fā)送是由串化器的SYNC1和SYNC2控制的,只要兩者之一置高電平持續(xù)時間超過6個時鐘周期,串化器就開始連續(xù)發(fā)送同步信號。快速同步具有快速準確的優(yōu)點,但在長距離的信號傳輸中,光纖只傳遞數(shù)據(jù),無法很好的傳遞串化器和解串器的SYNC和LOCK信號。因此采用隨機同步方式。隨機同步方式串化器不需發(fā)送同步信號,解串器直接對數(shù)據(jù)流進行鎖定,實現(xiàn)同步,鎖定丟失后,解串器會重新鎖定時鐘。將LOCK接到FPGA以進行實時控制。串/并轉(zhuǎn)換電路如圖8所示。

評論