基于VHDL語言的FPGA簡易數(shù)字鐘設(shè)計

作為一個菜鳥我很愿意分享下我做的一些小東西,記得一年前好像少幾天吧,看記錄是2009年5月19日

本文引用地址:http://www.104case.com/article/164887.htm我用51單片機做數(shù)字鐘的情景,那個時候用匯編,焦頭爛額,做了三天,還請教了老師。

哎,現(xiàn)在都已經(jīng)用C了,而且重心已經(jīng)放在了AVR上,

不過想想,這一年我還是學(xué)了很多東西,至少不是虛度了這一年。

FPGA是挺好玩的,不過沒有時間搞,忙著比賽。

不過憑借著學(xué)期前兩個禮拜實習(xí)天天晚上去圖書館自學(xué)VHDL的基礎(chǔ),加上單片機的基礎(chǔ),一直活到現(xiàn)在。呵呵呵

臭屁一下,今天老師說我可以做他的助教,確實把我興奮了一把,

其實我一直很心虛,因為都沒有時間搞,哪天出個難題答不上來就糗了。

今天中午和下午花了6個小時左右的時間做了一個數(shù)字鐘,

VHDL語言(Very high speed integrated circuit Hardware Description Language)即超高速集成電路硬件描述語言。

顧名思義既然是硬件描述,當(dāng)然是描述硬件,這個語言相當(dāng)于在FPGA或CPLD芯片里熔出一個數(shù)字電路。

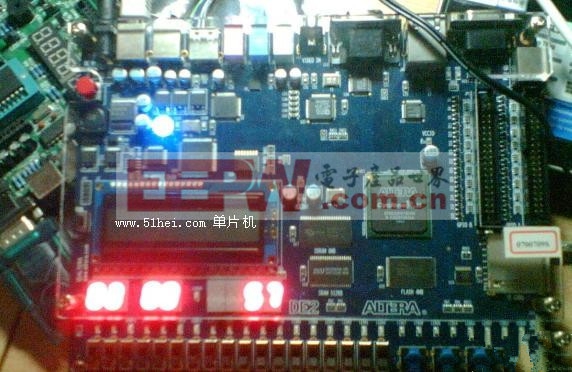

硬件FPGA 芯片是ALTERA公司Cyclone II 系列的EP2C35F672C6

使用的是ALTERA公司的開發(fā)板,型號DE2來張全圖,軟件為Quartus II 8.0,、ALTERA公司為自己產(chǎn)品打造的開發(fā)軟件。

據(jù)說是5000塊錢,因為是學(xué)校教學(xué)用,批量買,2500塊錢(不過我看下,就芯片貴,我看這個板子人家至少賺了1000多),我原來以為老師不會借,不過他似乎不介意,倒是他主動借給我的,額。。。

不費話了,貼程序吧

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity fpq is

port(clk : in std_logic;

k : in std_logic;

k1 : in std_logic;

k2 : in std_logic;

ge : out std_logic_vector(0 to 6);

shi : out std_logic_vector(0 to 6);

feng : out std_logic_vector(0 to 6);

fens : out std_logic_vector(0 to 6);

shig : out std_logic_vector(0 to 6);

shis : out std_logic_vector(0 to 6));

end fpq;

architecture first of fpq is

signal clock : integer range 0 to 24999999;

signal ge_t : integer range 0 to 9;

signal shi_t : integer range 0 to 5;

signal feng_t : integer range 0 to 9;

signal fens_t : integer range 0 to 5;

signal shig_t : integer range 0 to 9;

signal shis_t : integer range 0 to 2;

signal temp : integer range 0 to 9;

begin

t0: process(clk)

begin

if (clk'event and clk='1') then

clock = clock + 1;

if clock = 24999999 then

---------------------------------------------

if k='0' then

---------------------------------------------

if ge_t = 9 then

ge_t = 0;

if shi_t = 5 and ge_t = 9 then

shi_t = 0;

if feng_t = 9 and shi_t = 5 then

feng_t = 0;

if fens_t = 5 and feng_t = 9 then

fens_t = 0;

if shis_t = 2 and shig_t = 3 and fens_t = 5 then

shig_t = 0;

if shis_t = 2 and shig_t = 3 then

shis_t = 0;

else

shis_t = shis_t + 1;

end if;

else

if shig_t = 9 and fens_t = 5 then

shig_t = 0;

else

shig_t = shig_t +1;

end if;

end if;

else

fens_t = fens_t + 1;

end if;

else

feng_t = feng_t + 1;

end if;

else

shi_t = shi_t + 1;

end if;

else

ge_t = ge_t + 1;

end if;

else

if k1='0' then

if feng_t = 9 then

feng_t = 0;

if fens_t = 5 then

fens_t = 0;

else

fens_t = fens_t + 1;

end if;

else

feng_t = feng_t + 1;

end if;

end if;

if k2='0' then

if shig_t = 3 and shis_t = 2 then

shig_t = 0;

shis_t = 0;

else

if shig_t = 9 then

shig_t = 0;

if shis_t = 2 then

shis_t = 0;

else

shis_t = shis_t + 1;

end if;

else

shig_t = shig_t + 1;

end if;

end if;

end if;

end if;

------------------------------------------------

end if;

end if;

------------------------------------------------

end process t0;

c: process(clk,ge_t,shi_t,feng_t,fens_t,shig_t,shis_t)

begin

case ge_t is

when 9 => ge = 0000100;

when 8 => ge = 0000000;

when 7 => ge = 0001111;

when 6 => ge = 0100000;

when 5 => ge = 0100100;

when 4 => ge = 1001100;

when 3 => ge = 0000110;

when 2 => ge = 0010010;

when 1 => ge = 1001111;

when 0 => ge = 0000001;

end case;

case shi_t is

when 5 => shi = 0100100;

評論