Spartan 6上嵌入式網絡服務系統設計實現

摘要:隨著FPGA在嵌入式領域的快速發展和網絡技術的日益成熟,基于FPGA的網絡開發成為嵌入式系統研究的重要分支。本文系統地研究了FPGA網絡通信,并成功運用Xilinx開發平臺EDK構建一個基于總線AXI4的嵌入式網絡服務系統。系統包括硬件系統設計和軟件程序設計,即采用MicroBlaze微處理器軟核,Xilkernel嵌入式操作系統和lwip以太網協議,實現了通過Web瀏覽器對開發板的實時控制和網絡數據回傳的實時顯示。這一設計在Spartan 6 Atlys開發平臺上得以實現和驗證,為需要使用該系列開發板進行的網絡通信設計提供了很好的指導作用。

本文引用地址:http://www.104case.com/article/164385.htm引言

隨著嵌入式系統的發展和Internet的普及,越來越多的嵌入式系統引進Web Server和遠程等概念。以太網以其速度快、成本低,成為嵌入式Web Server和遠程文件傳輸接入網絡的主要方式。因此,實現基于以太網的嵌入式Web Server和遠程文件傳輸具有十分重要的實際意義。

本設計采用Spartan 6 XCSLX45芯片Atlys FPGA開發板,其具有容量大、資源多、性價比適中等特點,此外Atlys配備了各種高端接口,包括千兆以太網、HDMI視頻輸入輸出、128MByte DDR2存儲陣列、AC97 Codec及USB接口,其采用的是Marvell公司的千兆以太網(GbE)PHY收發器88E1111,支持GMII接口,GMII接口支持三種速度模式10/100/1000Mbit,這為本文的以太網通信提供了網絡通信條件。同時,AXI總線是ARM高級微控制器總線結構的一部分,擁有高產率、高靈活、廣泛IP可用性等優勢[1]。本文采用AXI4總線結合Atlys上的GMII接口,設計并實現了lwip以太網通信,為今后在嵌入式通信領域的進一步研究奠定了基礎。

系統的設計

本文將會從系統硬軟件兩方面的設計和實現進行闡述,本設計是基于Spartan 6 Atlys硬件開發平臺,利用Xilinx ISE 13.2軟件開發平臺進行硬軟件的設計,由于EDK集成的XPS(Xilinx Platform Studio)硬件設計平臺和SDK(Xilinx Software Development Kit)軟件設計平臺,本文的lwip以太網通信嵌入式系統的設計將會分成硬軟系統設計兩部分進行詳細地介紹。

硬件系統的設計

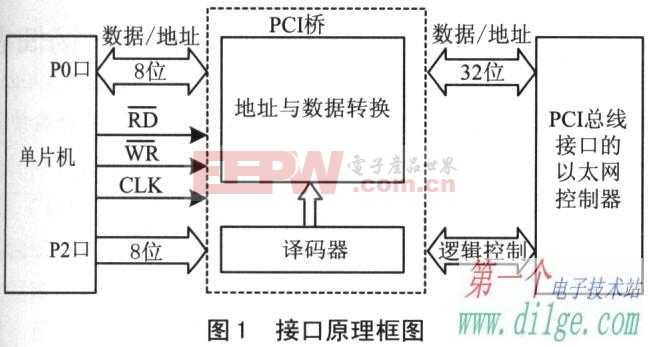

本系統的總體硬件設計如圖1,包括AXI總線,MicroBlaze CPU核,Ethernet為設計千兆以太網,Ethernet_dma為實現Ethernet和MCB_DDR2的快速數據傳輸,MCB_DDR2 128MByte存儲陣列,axi_intc,axi_timer時鐘控制模塊,LED_8Bits 8個LED燈,RS232_Uart串口控制器,Debug_Module以及Dip_Switches_8Bits 8個撥碼開關,采用100MHz時鐘。

系統間的數據交互是通過千兆以太網實現的[2],下面對關鍵IP核:AXI_DMA、Ethernet IP核[3]進行簡要的介紹。

ETHERNET_dma即AXI_DMA(AXI直接內存訪問),是Xilinx嵌入式開發套件(EDK)中自帶的IP軟核,它為內存和AXI流型目標外圍設備提供高帶寬的直接內存訪問,它通過從CPU上卸載數據移動任務來體現分散/收集功能,如AXI以太網之間提供高速數據移動。

Ethernet核通過32位的AXI4-Lite接口子集為內部寄存器提供了一個控制接口,AXI4-Lite接口支持單拍讀和寫的數據傳輸(無突發傳輸)。發送和接收數據接口都是通過AXI4-Stream接口。AXI Ethernet通過AXI4-Lite總線接口連接到MicroBlaze處理器內核上,允許訪問寄存器,同時32位AXI4-Stream總線可供以太網數據在AXI Ethernet上發送和接收。在硬件沒有負載條件下,該AXI4-Stream總線提供TCP/UDP的部分校驗和。

由于本設計中使用Spartan 6 Atlys系列,本文為該系列的網絡通信研究提供的方法:使用Soft Ethernet IP核,設置使用GMII模式,該IP核是soft TEMAC需要特定的license,可在官方網站上下載。Ethernet核可以計算發送TCP/UDP校驗和以及驗證發送TCP/UDP校驗和,使用此邏輯可以顯著地提高最大以太網總線數據傳輸率,同時降低處理器對以太網任務的利用率。系統的MicroBlaze微處理器通過AXILITE總線接口訪問AXI DMA,分散/收集引擎從MCB_DDR2中查找緩沖區描述符,然后協調AXI Ethernet和MCB_DDR2之間的主要數據傳輸。例如MCB_DDR2中的參數設置:

PARAMETER C_INTERCONNECT_S0_AXI_MASTERS = microblaze_0.M_AXI_DC & microblaze_0.M_AXI_IC & ETHERNET_dma.M_AXI_SG & ETHERNET_dma.M_AXI_MM2S & ETHERNET_dma.M_AXI_S2MM

以及Ethernet中的接口設置:

BUS_INTERFACE AXI_STR_TXD = ETHERNET_dma_txd

BUS_INTERFACE AXI_STR_TXC = ETHERNET_dma_txc

BUS_INTERFACE AXI_STR_RXS = ETHERNET_dma_rxs

BUS_INTERFACE AXI_STR_RXD = ETHERNET_dma_rxd

通過上述設置和IP核的加入,一個基于AXI4總線lwip以太網嵌入式硬件系統搭建完畢,在Xilinx XPS硬件系統設計工具中修改相應的ucf約束文件,即可通過Hardware->Generate Bitstream產生比特流文件供后續軟件系統設計的調用。

軟件系統的設計

本文的軟件系統主要分為三部分:文件系統的建立、FTP遠程傳輸文件設計以及HTTP(超文本傳輸協議)服務[4]利用網頁對Atlys開發板進行遠程顯示及實時控制的設計,從而使傳統控制設備轉變為具備了以TCP/IP為底層通信協議,Web技術為核心[5]的Internet控制設備。軟件系統采用Xilinx ISE集成的Xilkernel系統內核,通過設置選擇相應的庫文件,如本文所需要的lwip130(用于輕量級以太網的通信,TCP/IP協議的一種,并且了解了輕量級TCP/IP協議棧和一般操作系統的TCP/IP協議棧的區別[6])和xilmfs(用于文件存儲系統)的庫文件,設計程序時調用所配置系統的庫文件、系統頭文件以及自定義的一些程序文件,從而設計出完整的lwip以太網通信系統。

tcp/ip相關文章:tcp/ip是什么

評論