掃頻接收機中數字掃描控制器設計

掃描控制基本流程如下:

1)程序首先計算各控制量的分段數目及段內各控制量的起始值、步進值、步進個數。

2)通過系統總線,程序將上述計算好的數據依次送入掃描控制器內的RAM中保存。

3)程序控制觸發單元產生全局中斷信號,由中斷處理單元通知運算單元讀取各控制量首段的初始值。

4)程序控制觸發單元產生使能信號,控制步進脈沖發生單元產生計數脈沖。這時運算單元開始進行累加/減計算并且計數器記錄已產生的脈沖個數。累加/減運算器的輸出值通過D/A變換器轉換為電壓值控制相關硬件電路。

5)當運算單元內計數器的計數值達到本段設定的步進個數時,運算單元產生中斷信號通過中斷處理單元進行中斷識別并通知運算單元內已產生中斷的模塊自動從RAM內讀取下一段的初始值。運算單元內四個模塊產生中斷的中斷級別各不相同,如果多個中斷同時產生,那么中斷處理單元會對各中斷進行緩存、排序并且首先處理中斷級別高的中斷。

6)當下一個計數脈沖到來時,運算單元內產生中斷的模塊又會重新開始累加/減運算并計數,重復4、5步。

7)觸發單元記錄掃描時間。當掃描時間達到預設值時,觸發單元控制使能信號為低電平,各寄存器復位,掃描過程結束。

3 模塊內部實現

1)地址譯碼/數據緩存單元地址譯碼/數據緩存單元連接外部總線,通過譯碼接收屬于本掃描控制器的數據和控制字,包括:復位控制字、掃描使能控制字、觸發單元內計數器的計數值(用于計算掃描時間)、步進脈沖發生單元內計數器的計數值(用于產生步進脈沖)以及RAM內需存儲的控制量DAC值。

2)RAM存儲單元

存儲控制量DAC值。如果接收機內地址資源足夠豐富,軟件可以通過地址譯碼/數據緩存單元直接訪問RAM。如果接收機內地址資源有限,可以將整個RAM劃分為若干個區域(段地址),每個區域對應于一種控制量。每種控制量的各分段數據依次排列,可通過段內偏移地址訪問。

3)運算單元

運算單元包括RAM數據回讀模塊、計數器及累加/減運算器模塊。RAM數據回讀模塊的回讀方式取決與RAM內數據的存儲格式;計數器通過將讀取的步進個數值與當前的計數值進行比較決定是否產生中斷。在實際應用中,累加/減運算器位數有限,而計算的步進DAC值位數有可能大大超過運算器位數,這就要求設計人員必須認真選取步進DAC的有效長度,對DAC值進行適當截取,使控制誤差能夠在可接受的范圍內。累加/減運算器模塊在步進脈沖的觸發下,對初始值進行累加/減運算,其DAC值輸出位數等于選甩的DAC器件位數。

4)D/A輸出單元

D/A輸出單元負責將已累加/減數據轉換為模擬信號輸出。D/A輸出單元時序同步于控制脈沖。如果掃描控制器硬件資源不多,可以給每一個控制量單獨配置一個D/A轉換器;否則,可以將這些控制量先緩存起來再通過一個D/A轉換器輸出以減少硬件成本。

5)觸發單元

觸發單元接收到掃描使能控制字后控制步進脈沖發生單元使能端有效,步進脈沖發生單元開始工作,進而使得整個掃描控制器運轉起來。當觸發單元內計數器的計數值與接收到的用于計算掃描時間的計數量相同時表明掃描過程已經完成,這時觸發單元控制步進脈沖發生單元使能端失效,步進脈沖發生單元停止工作,掃描過程結束。另外,在掃描開始前觸發單元接收控制字產生全局中斷信號,通過中斷處理單元通知運算單元調用各硬件控制量的初始DAC值。

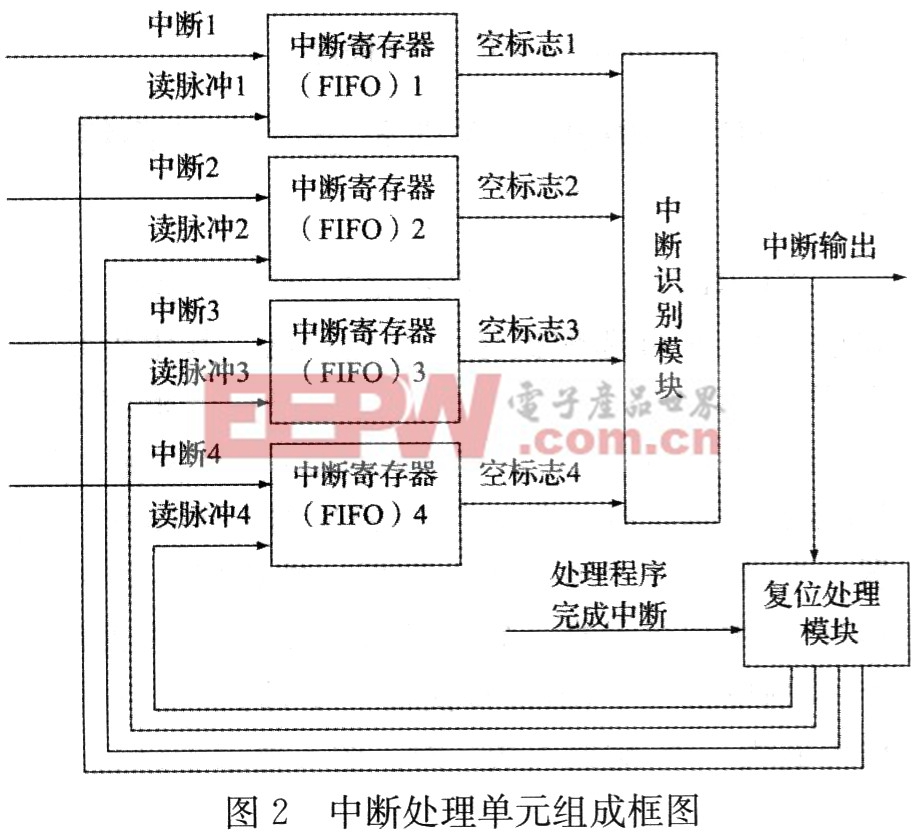

6)中斷處理單元

中斷處理單元根據預先設定的中斷優先級別決定控制運算單元內各模塊的先后順序。中斷處理單元由中斷寄存器、中斷識別模塊、復位處理模塊三部分組成。組成框圖見圖2所示。

評論