基于FPGA的智能溫度采集控制器

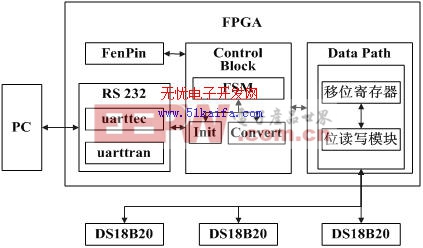

針對溫度采集控制器系統的特點,決定采用自上而下的設計方法,并將整個系統分為Control Unit和Data Path來進行設計(圖1)。這樣實現有以下優點:(1)Control Unit在內部FSM的控制下,在每一個State會有Outputs,控制Data Path中數據的傳輸,滿足DS18B20的時序要求;(2)Data Path則完成了所有的數據流傳輸,并實時的反饋給Control Unit一些Inputs,從而使其State轉換能夠正確完成;(3)如果要有附加的控制流和數據流要添加進整個FPGA系統,則只要在Control Unit中更改相應的State和Data Path中做相應修改就可。這樣設計出來的系統穩定、擴展性好。

圖1、智能溫度采集器的系統結構框圖

在設計Control Block的時候一般采取有限狀態機(FSM)的方法。FSM分兩大類:米里型(Inputs對輸出邏輯和下一狀態邏輯有影響)和摩爾型(Inputs只對下一狀態邏輯有影響)。FSM設計中首要的是確定狀態變量。這是以對設計問題的深入了解為基礎的。每一個狀態都有可以實現的進入條件,每個狀態在所有輸入條件下都有明確的下一狀態,包括下一狀態和目前狀態相同的狀態的情況。顯然,如果下一狀態只有和目前狀態相同的狀態才是可實現的,那么FSM一旦進入這個狀態就不會再改變了,這種“死機”狀態當然是要避免的。在此系統的 Control Block中的FSM采用摩爾型,設計出“下一狀態邏輯”從而使得“狀態寄存器”能在每一個時鐘沿正確的進行狀態轉換,并確定好“輸出邏輯”,在每一個狀態都能輸出正確的控制流來對 Data Path中的數據流進行正確的控制,保證整個系統能夠正確的工作。

數據通道實現的是數據間的運算和傳輸。數據可能是8/16/32/64位的,一般所有位的運算并沒有太大的不同。但是,它又要同時實現Control Block中的FSM的功能,其設計是要和 Control Block中的FSM的結構一起考慮的。一旦FSM確定了,數據通道的計劃就要著手進行。由于數據通道的性能決定了整個系統的性能的高低,所以它又非常的關鍵。以往通用處理器因為生產數量大,數據通道用全定制的方法設計比較多,線路和版圖設計的精雕細刻,以求換得低的芯片生產成本和用其他方法難以達到的性能水平。這種情況在現代的SOC產品里有了很大的改變,因為SOC產品的產量一般都比較小,而且設計者都希望同一個處理器核的設計能夠用于不同工藝生產的產品。這樣,全定制的設計就不合適了。一般來說,數據通道是一定形式的流水線,因為數據的讀取、運算和結果的寫入都在同一個周期內實現,時鐘頻率就很難提高,所以高性能處理器的數據通道現在都采用流水線設計。數據通道和數據寄存器和數據存儲器的關系十分密切,這當然是由處理器的結構確定的。在此系統中的 Data Path的數據流處理功能并不是非常的復雜,可以不用采取流水線設計,并在FSM的控制下進行正確的數據流傳輸,同時會反饋給FSM中的“下一狀態邏輯”一些Inputs信號來使其能夠進行正確的狀態轉換。

評論