基于FPGA的IRIG-B編碼器實現

(5)在PPM12的上升沿根據第3.1節所得碼元計數器MMH重新加載CMP

算法VHDL描述如下:本文引用地址:http://www.104case.com/article/163206.htm

在上述VHDL編碼的實現中,MSCLK為1 ms計數脈沖.同步于PPM12信號的上升沿。CMP的輸出值由函數IRIG_B根據輸入參數決定,若為0,則輸出“0000000011”,對應2 ms;若為1則輸出“0000011111”,對應5ms。在索引脈沖和參考點Pr處,CMP取值“0011111111”,對應8 ms。而最終的編碼輸出IRIG_B_0UT在每個1 ms脈沖的上升沿,根據CMP(MML)的值決定為高或為低。

4.2 IRIG-B AC編碼模塊

4.2.1 數字調制原理

按照奈奎斯特抽樣定理,只要抽樣頻率高于2倍信號的最高頻率,則整個連續信號就能完全用它的抽樣值來代表。使用抽樣值構成的序列經DAC和低通濾波后即可恢復原來的連續信號。

若對頻率為f的正弦波抽樣N次(N>2f),并在T=1/f內通過DAC等間隔輸出N次抽樣值,則低通濾波后可恢復原始正弦信號。各個采樣點值為:

4.2.2 正弦查找表

這里給出利用查找表實現交流數字調制的方法。在獲得IRIG-B的直流編碼后,將該信號導入到數字調制模塊,即可獲得交流編碼。對正弦信號進行100次等間隔抽樣,對式(2)使用實際的增益和直流偏移,可得式(3)。據此獲得查找表。

式中:N=100為采樣率;k=O,1,2,…,N-1;Ck對應第k次抽樣獲得的值;A0為保證輸出信號為單極性而設置的初始直流偏移;Ac為考慮調制比和DAC滿幅度碼值的系數。

由于交流信號頻率為1 kHz,周期為T=1 ms,若在1 ms內將上述抽樣值等間隔輸出到DAC,即可獲得1 kHz的調制信號。

本文使用MAX5712和單電源rail-rail運放AD8601構成濾波器。在MAX5712滿幅輸出時,C=4 095(12 bit DAC),選擇調制比為1∶5。綜合考慮,在最大輸出時,不能使DAC輸出到達運放的上軌,最低輸出時,DAC輸出應高于運放的下軌,所以選取A0=C/2+200=2 248。對應邏輯0,Ac=461;對應邏輯1,Ac=1 844。根據上述原則計算出的正弦查找表如表1所示。

實際使用時,應根據使用DAC的解析度、運放的動態范圍以及采樣率及調制比確定上式中的參數。

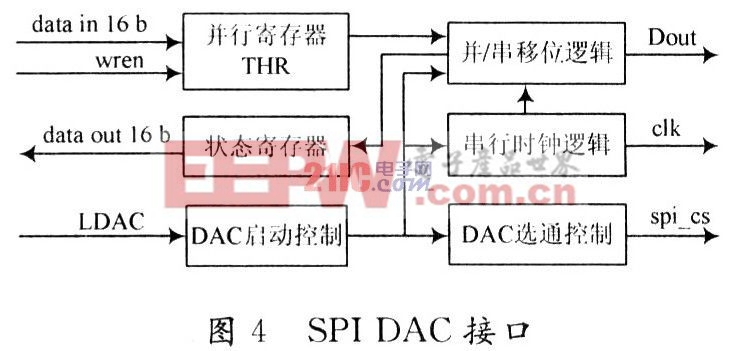

4.2.3 DAC接口

實際使用時應根據DAC的不同,在FPGA中構建不同的數字接口。MAX5712需要在FPGA實現一個SPI接口,結構如圖4所示。接口控制部分提供一個16 b寫端口,可以接收數據。在寫使能wren為高時,接口上的數據寫入內部并行保持寄存器。在LDAC脈沖的上升沿,并行寄存器THR的內容寫入移位寄存器,同時啟動時鐘邏輯。在輸出時鐘作用下,數據從Dout輸出到DAC,在SPI_CS的后沿,DAC啟動轉換輸出與當前編碼相匹配的模擬量。

評論