車載電子羅盤中的一種新型抗干擾設計

ADXL202E輸出的信號占空比調節(DCM)周期由外接電阻決定,一般低于1 kHz,因此計數輸入端高低電平持續時間長達幾ms甚至幾十ms,可見傳感器輸出的正常計數信號高、低電平變化較慢;而控制器脈寬計數時間小于1μs,干擾尖峰脈沖是突變的,所以能把干擾從正常計數中辨別出來。因此,使用軟件濾波來消除尖峰脈沖干擾是可行的。

VRS51L3074單片機是由美國Ramtron(瑞創)公司推出的8位單片機家族VRS51L3xxx系列的成員。VRS51L3074提供了2個與定時器O和1關連的獨立的脈寬計數器(PWC)模塊,用戶可通過對PWC模塊和定時器的配置,靈活地控制定時器啟動或停止計數,從而方便地實現對ADXL202E輸出的脈寬和周期的計數。

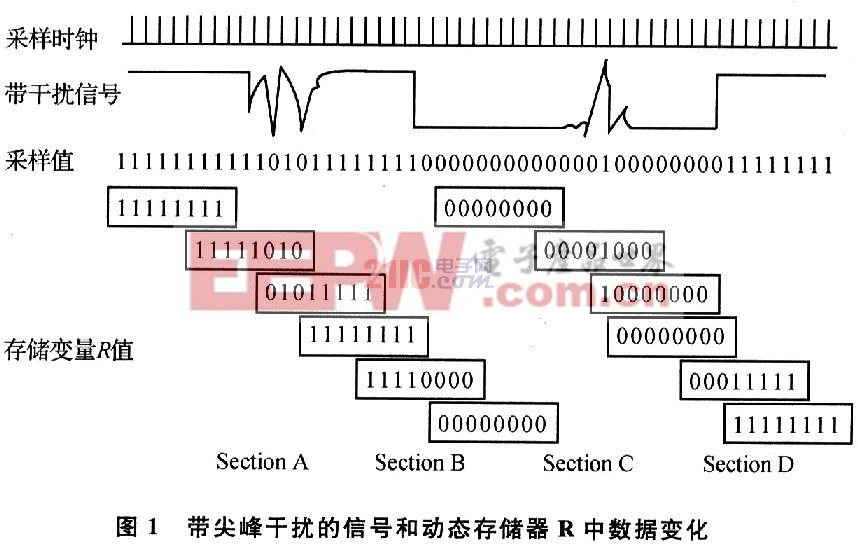

從單片機計數輸入端,觀察信號波形。為便于分析,在高、低電平段設置了幾個干擾尖峰脈沖,分別標示為Section A和Section C,占空比信號下降沿、上升沿分別標示為Section B和Section D。單片機按計數時鐘周期性采樣,采樣值中“1”表示采到的是高電平,“O”表示低電平。I/O口采樣占空比信號輸出端口中狀態,利用1個字節型變量R來動態存儲采樣值。控制器每采樣1次,變量R中數據向左移1個二進制位,R原最高位電平狀態被移除,而當前時刻新的采樣狀態保存到R的最低位,變量R被更新了,狀態存儲器R中保存著最近8個采樣周期的采樣值。本文引用地址:http://www.104case.com/article/163019.htm

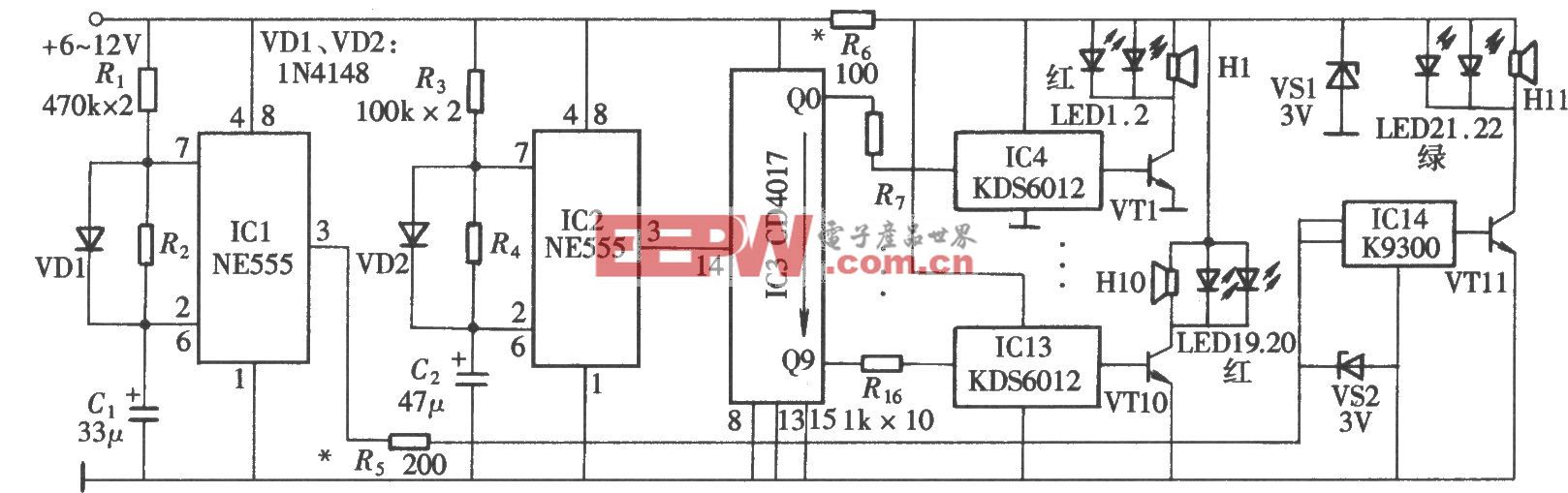

在圖1中,從正常下降沿過程(Section B),可以看到變量R中的數據經歷了從各位全為1,到1、O共存,再變化到全為O的過程;然而,在高電平段的干擾部分(Section A),變量R經歷了從全為1,到1、0混合,再回到全為l的過程。類似地,正常上升沿(Section D)變量R經歷了各位全為0,到O、1共存,再變化到全為1的狀態變化過程;在低電平段的干擾部分(Section C),變量R經歷了采樣狀態從全為O,到O、1混合,再回到全為O的過程。通過判斷此4種情況下變量R中數據的不同變化過程,可以達到從正常變化中辨別出干擾的目的。這就是本設計所采用的軟件濾波抗干擾方法的基本思想。

3 軟件濾波算法的實現

3.1 軟件濾波分析

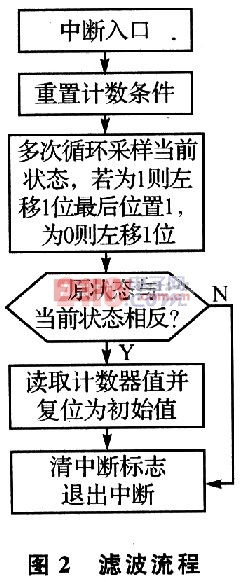

根據軟件濾波設計思想,濾波子程序由主程序在信號狀態發生變化,進入中斷時調用,圖2給出了濾波程序流程。對照圖1中4種Section來分析流程圖。當有邊沿或干擾信號(信號周期大于計數時鐘周期)到來時,VRS51L3074單片機的PWC計數停止條件滿足,系統進入中斷服務子程序。在中斷子程序中,首先重置脈寬計數條件,然后對當前狀態進行采樣,采樣1次,狀態寄存器左移1位,采樣到高電平記為“1”,采樣到低電平記為“O”。如正常下降沿Section B,前面處于高電平段,初始狀態變量Flag全為1,當出現低電平,控制器進入中斷,緊接著進行16次采樣。前已提及系統處理的尖峰干擾約1~2 ms,每個采樣周期約為O.4 ms,其尖峰干擾脈寬達不到8個采樣周期。系統設計時采樣16次,只取最后8次的存儲狀態與原狀態進行比較,如果最后采樣的狀態全為“O”則與原狀態相反,就可判斷出這是1個正常下降沿。如果是干擾信號引起計數中斷,前面8個采樣狀態不全為“1”,后面8個狀態全為“1”,最后采樣的狀態與原狀態相同,就可判斷出這是1個干擾信號,如Section A。在信號狀態采樣期間,計數條件滿足PWC繼續計數,直到真正的下降沿到來,計數停止并保存,計數寄存器還原為初始值,這樣干擾信號即被濾除。類似地,正常上升沿Section D,存儲器原狀態為“O”,上升沿來臨后存儲器狀態為“1”,與原狀態相反,PWC計數停止并保存,計數寄存器還原為初始值,退出中斷子程序。有干擾信號出現后采樣狀態與原狀態相同,干擾尖峰脈沖可被濾除。如果要使脈寬計數更精確,可判斷前8個采樣周期中系統不正常計數的周期,然后與最終計數周期相加即可。此時,程序流程體現出軟件濾波功能。

評論