X光安檢機控制信號時鐘提取的設計與實現

4 FPGA硬件測試

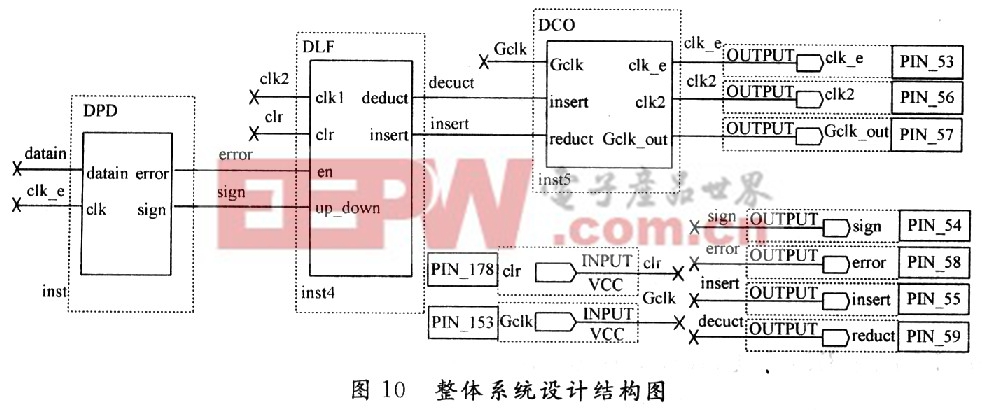

鑒于該系統應用于安檢機控制信號傳輸系統中,故將該設計通過FPGA硬件平臺進行了驗證。該驗證平臺基于Altera公司Cyclone系列的EPlCl2Q240C8型號的FPGA芯片。鑒于實際系統中FPGA的本地系統時鐘為32.768 MHz,故測試輸入數據(datain)的速率為4.096 MHz。基于FPGA開發軟件Quartus實現的測試系統整體結構圖如圖10所示。本文引用地址:http://www.104case.com/article/162981.htm

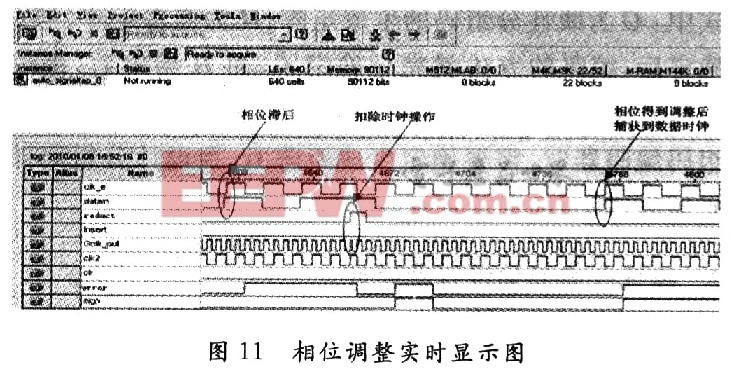

Signal TapⅡ邏輯分析器是Quartus軟件中集成的一個內部邏輯分析軟件,使用它可以觀察設計的內部信號變化,為FPGA設計的調試、開發帶來極大的方便,實用性很高。以下各圖為Quartus軟件中SignalTapⅡ實時觀察到的數據。

相位調整驗證如圖11所示。由圖11可以發現,開始時鐘的相位滯后于數據相位。因此經過調整,通過數字環路濾波器輸出的reduct信號控制數控振蕩器模塊進行扣時鐘操作,最終使本地估算時鐘與數據時鐘同步,正確地調整了相位。

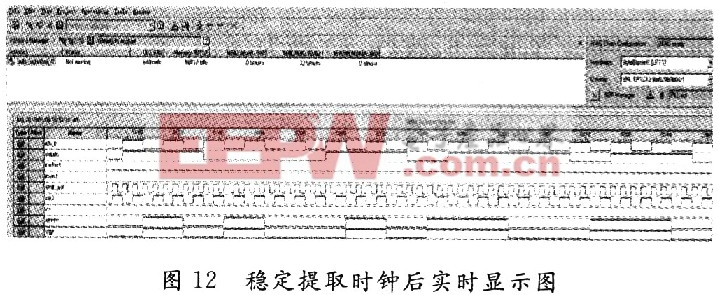

當該系統捕獲到數據時鐘后,就會穩定輸出與數據信號同相的時鐘信號,穩定狀態截圖如圖12所示。

利用FPGA開發平臺所具有的Signal TapⅡ功能,成功地在硬件平臺上驗證了該系統的可行性與穩定性。

5 結語

目前,鑒于國際國內形勢的發展,安檢機系統得到了越來越廣泛的應用,安檢機中通信系統的發展也逐漸趨向高速化、高效化。對于采樣數據量的增大,就要求有一條高速傳輸通道,同時,控制臺低速控制信號的傳輸也要求有高效鏈路的構建。本文設計了一個高效時鐘提取方案,并在FPGA上完成了驗證。實驗結果表明,基于鎖相環的實現方案不僅提高了時鐘提取的精度,而且平衡了捕捉時間,為安檢機系統低速控制信令的傳輸提供了基本的技術支持,并且使控制信號的傳輸僅需要一條數據線就可以完全實現,保證了安檢機控制信號鏈路傳輸的高效性,降低了設備成本,加快了開發速度,提高了整體系統的運行效率。

評論