X光安檢機控制信號時鐘提取的設計與實現

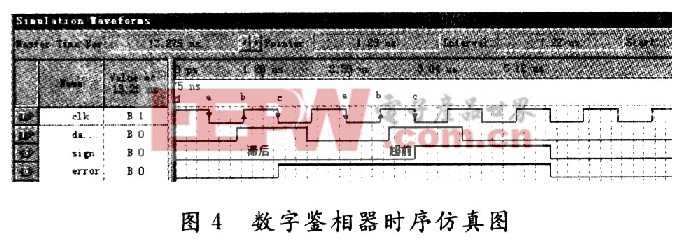

從圖4可以發現,對于error信號,若前一位數據存在跳變,則輸出高電平,否則輸出低電平。對于sign信號,當估算時鐘超前時,輸出高電平,滯后時,輸出低電平。該模塊輸出的兩路信號將作為環路濾波器的輸入信號,對下級結構進行控制。

2.2 數字環路濾波器

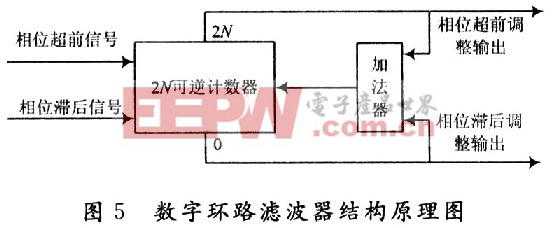

數字環路濾波器在鎖相環路系統中主要起兩種作用:其一,輸出超前調整信號及滯后調整信號,以控制數控振蕩器模塊,對估計時鐘進行相位調整;其二,有數字濾波作用,對噪聲信號及高頻干擾信號起到較好的抑制作用。數字環路濾波器內部擁有容量為2N的計數器,能夠有效消除隨機出現的具有正態分布特性的噪聲信號。容量2N值越大,對噪聲抑制效果越好,但同時2N值越大,跟蹤速度越慢,實時捕捉能力下降。所以設計時,2N值的選取要綜合考慮安檢系統的實際參數要求。出于減少占用FPGA系統資源的考慮,該系統采用隨即徘徊濾波器作為實現方案。該濾波器原理框圖如圖5所示。

在實現方案中,環路濾波器通過加減計數邏輯單元實現。通過讀取鑒相單元輸出的兩路使能信號對計數器進行代數累加或累減操作,當達到記數的邊界值0或2N時在輸出端送出insert(插入時鐘周期)或deduct(扣除時鐘周期),與此同時,計數器內部寄存器值從2N自動恢復到N,重新開始。

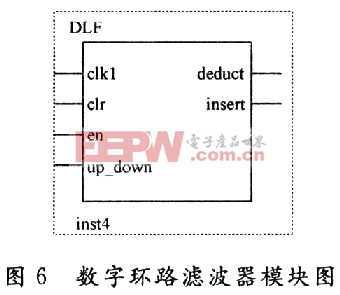

該模塊如圖6所示,其中clkl是記數時鐘,由數控振蕩器模塊內部分頻得到;clr是啟動清零控制端;en接前端模塊的error信號,該引腳是對記數功能的使能,即在輸入數據(Data_in)有跳變時,才能判斷相位誤差;up_down是加減記數輸入,與上級模塊的sign使能信號相連,當sign=1時,做累加操作,當sign=0時,做累減操作,直到代數累加/累減運算到0或2N時,再對累加/累減計數器進行恢復。

評論