基于FPGA的LED大屏幕控制系統的設計與實現

2 SDRAM乒乓式緩存的優化

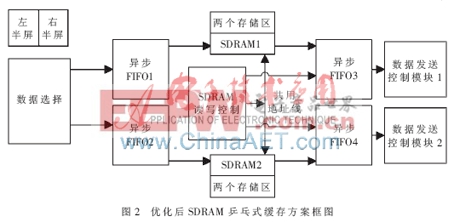

傳統的基于SDRAM的乒乓式緩存方案[1,2]都存在著數據讀寫操作復雜或者數據結構調整局限性大的缺點。結合現有方案的優點,本文提出了圖2所示的SDRAM數據緩存方案。本文引用地址:http://www.104case.com/article/162722.htm

本系統的發送卡設計目標是最大支持1 280×1 024分辨率、60 Hz刷新率的全彩數據發送,此時的像素頻率為:

即本方案滿足系統數據吞吐量的要求。由于兩個SDRAM中存儲相同數據,具有相同格式,所以SDRAM讀寫模塊可以同時向兩個SDRAM中寫入或讀出顯示數據,這樣兩塊SDRAM可以共用地址線,從而節省數十個FPGA IO端口,這是本方案的一大優點。同時每塊SDRAM中劃分了兩個區,用以存放連續的兩幀圖像,可以根據LED顯示屏的具體要求,從SDRAM中讀出顯示數據,滿足系統靈活性的要求。

3 反γ校正與灰度級調節

特定條件下創建的圖像在不同環境下工作時,往往會出現圖像看起來顯得太亮或者太暗的現象,所以LED大屏幕顯示系統需要進行靈活的反γ值調節。當前反γ校正多采用基于FPGA內部ROM的查找表技術[3]。式(1)為反γ校正公式,式中默認輸入圖像灰度級為256,輸出灰度級為G,x為輸入灰度值,y為輸出灰度值,γ為校正系數。要在FPGA中實現指數運算需要消耗大量邏輯單元,對于低成本要求來說是不現實的。本文提出了如圖3所示的基于FPGA片內RAM、片外EEPROM和PC機軟件的反γ校正技術。

評論