基于nRF24L01和Actel FPGA的智能探測系統設計

2.2 Core 80515架構

Core 8051S是Actel公司推出的基于APB3總線的8051lP核,兼容8051的全部指令,同時又具備許多51單片機所沒有的獨特功能:

(1)具有可配置的JTAG接口調試功能,可利用Flash_Pro下載器作為其調試工具;優化指令執行速度,內部設置流水線,可實現單個時鐘周期執行一條指令,且是普通51單片機的12倍。

(2)采用APB3外設總線結構和SER寄存器內存映射方式管理外設,將外部擴展的64 KB數據空間中的最高4 KB作為APB3外設的寄存器內存映射地址,每個APB3外設占據256 B的地址,因此最多可添加16個外設。

(3)使用CoreConsole軟件以圖形化界面的方式添加Core8051S以及其他外設,既直觀又方便。

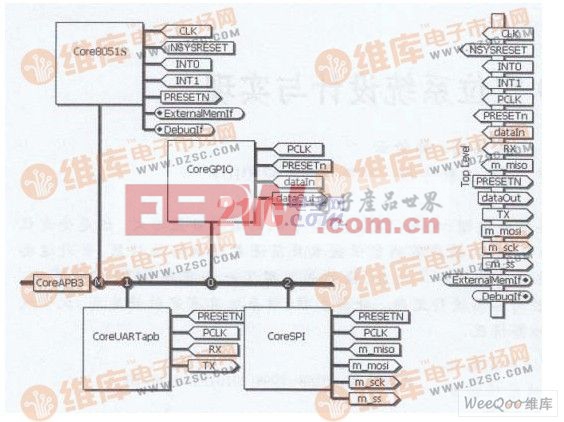

圖3是以CoreConsole開發的、基于Core805lS和APB3總線的50PC系統的典型架構。該軟件的開發流程與Altera公司基于NIOS Ⅱ處理器的soPc開發流程類似,同時又具有其獨特優勢:在系統不復雜、控制部分遠多于計算處理時,使用Core805⊥s可靈活迅速地進行開發,通過安裝ISA—Actel5 1為Keil提供調試驅動可直接使用Keil編寫代碼并進行在線程序調試,而優化后的指令執行速度可滿足大部分應用的要求。

圖3 CoreConsole下基于Core8051S的開發實例

本系統設計步驟:

(1)利用CoreConsole以圖形化方式設計片上系統所需的總線及外設,包括SPI、PWM、GP10、UART等模塊;配置各模塊與APB3總線之間的連接關系,正確分配外設地址;然后生成.Ⅴ文件導人Actel集成開發環境Libero。

(2)使用Libero的Flash Memory System Builder將Fu_S10n內部的Flash模塊配置為Core8051S的外部程序空問。如果有必要還可以將Fusi。n StartKit開發板上的SRAM作為Core8051S的外部數據空間使用。

(3)將工程編譯綜合后下載到開發板上,通過Keil編寫程序并進行調試。

評論