基于PCI Express總線(xiàn)的高速數(shù)據(jù)傳輸卡設(shè)計(jì)與實(shí)現(xiàn)

本文引用地址:http://www.104case.com/article/162618.htm

在上面的配置原理圖中有兩個(gè)下載口:一個(gè)是JTAG下載口,一個(gè)是AS下載口。其中JTAG下載口是用來(lái)下載.sof文件的,下載.sof文件后可以使用quartus II 6.0的邏輯分析儀進(jìn)行在線(xiàn)調(diào)試;另一個(gè)下載口是下載.pof文件的,其作用是把程序燒寫(xiě)進(jìn)EPCS4配置芯片,在FPGA每次加電開(kāi)始工作之后,把程序?qū)б紽PGA的內(nèi)部RAM中,使器件實(shí)現(xiàn)設(shè)計(jì)者要求的邏輯功能。

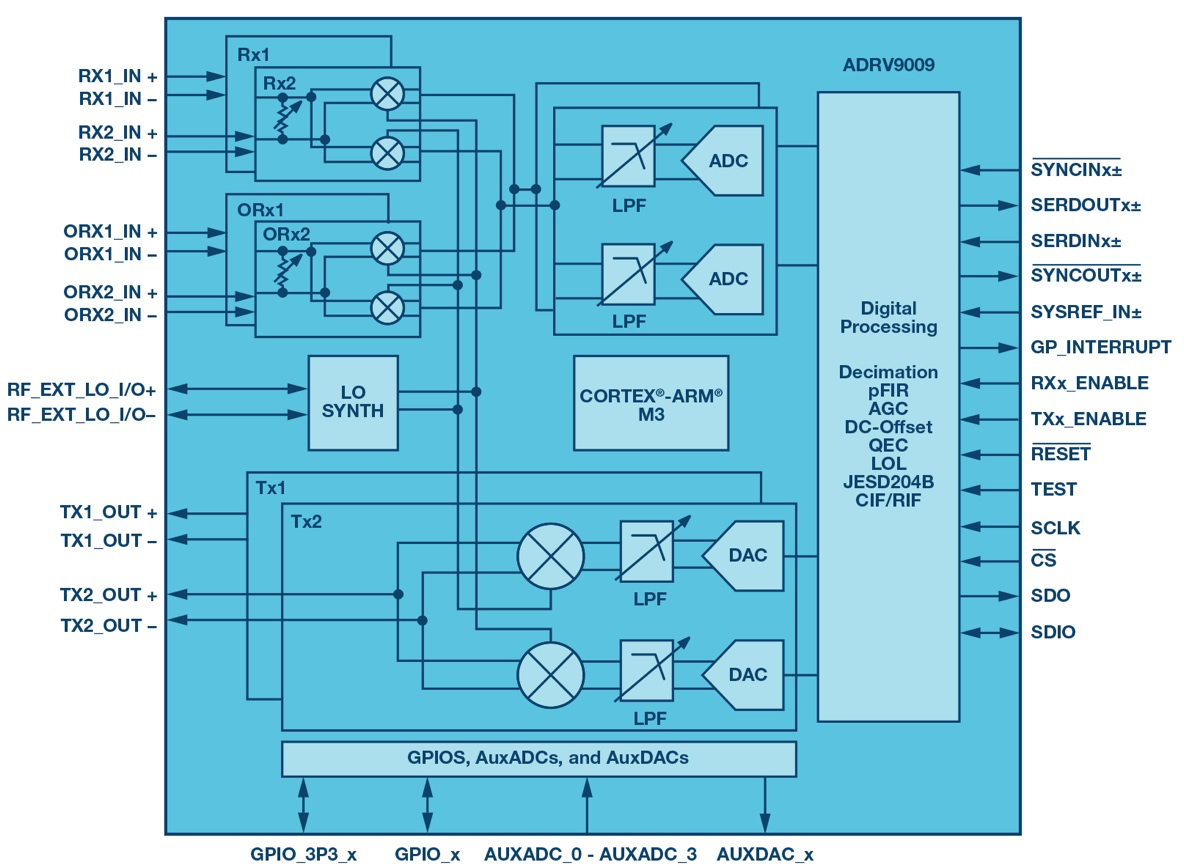

FPGA作為本地總線(xiàn)的邏輯控制器,負(fù)責(zé)協(xié)調(diào)好與FIFO和PEX8311之間的時(shí)序關(guān)系。系統(tǒng)接收數(shù)據(jù)時(shí), 首先由驅(qū)動(dòng)程序向PEX8311發(fā)送復(fù)位信號(hào),通過(guò)LRESET復(fù)位本地端的FPGA和FIFO,清空FIFO內(nèi)部數(shù)據(jù),并將HF和FF標(biāo)志置為無(wú)效,然后等待數(shù)據(jù)的輸入。數(shù)據(jù)和時(shí)鐘進(jìn)入FPGA后, 首先將外界傳入到FPGA中的16位并行數(shù)據(jù)在兩個(gè)CLK周期下合并為32位并行數(shù)據(jù), 并在每一個(gè)寫(xiě)時(shí)鐘WCLK的上升沿寫(xiě)入FIFO2。當(dāng) FIFO2中的數(shù)據(jù)達(dá)到半滿(mǎn)狀態(tài)時(shí), HF標(biāo)志位有效,通過(guò)FPGA向PEX8311發(fā)出DMA中斷請(qǐng)求。PC機(jī)響應(yīng)中斷后, 設(shè)置 DMA傳輸模式, 傳輸字節(jié)數(shù)及地址信號(hào)等。PEX8311通過(guò)LHOLD申請(qǐng)控制本地總線(xiàn), 待收到FPGA發(fā)出的 LHOLDA響應(yīng)信號(hào)后獲得本地總線(xiàn)的控制權(quán), 并立即啟動(dòng)4字節(jié)突發(fā)模式的Block DMA周期。FPGA在收到有效的LW/R讀信號(hào)和ADS地址選通信號(hào)后, 發(fā)出Ready本地準(zhǔn)備好應(yīng)答信號(hào), 同時(shí)使能FIFO2的讀允許 REN和輸出允許OE。在傳輸最后一個(gè)數(shù)據(jù)時(shí), PEX8311發(fā)出BLAST信號(hào), FPGA置FIFO讀使能和輸出使能無(wú)效, 并取消Ready從而結(jié)束DMA周期。系統(tǒng)發(fā)送數(shù)據(jù)時(shí),F(xiàn)PGA將計(jì)算機(jī)寫(xiě)入FIFO1中的32位數(shù)據(jù)拆分成兩個(gè)16位數(shù)據(jù)送入并串轉(zhuǎn)換芯片再經(jīng)過(guò)驅(qū)動(dòng)芯片發(fā)送到測(cè)試臺(tái)。

3 軟件設(shè)計(jì)

本系統(tǒng)軟件設(shè)計(jì)包括驅(qū)動(dòng)程序和應(yīng)用程序兩部分。為了降低開(kāi)發(fā)難度、縮短時(shí)間,又不使所開(kāi)發(fā)的驅(qū)動(dòng)程序效率太低,本文選用DriverStudio來(lái)開(kāi)發(fā)PCI-E的功能驅(qū)動(dòng)程序。應(yīng)用層軟件采用VC++6.0編寫(xiě),按用戶(hù)要求運(yùn)行于Windows2000/WindowsXP平臺(tái)。通過(guò)和人機(jī)交互界面接收用戶(hù)的設(shè)置,然后把這些設(shè)置傳遞至驅(qū)動(dòng)程序中,由驅(qū)動(dòng)程序?qū)τ布M(jìn)行初始化和配置,最后應(yīng)用程序從驅(qū)動(dòng)程序中讀寫(xiě)數(shù)據(jù)。本應(yīng)用程序采用了多線(xiàn)程的方式與驅(qū)動(dòng)程序進(jìn)行交互通信。

4 性能測(cè)試

信號(hào)源的數(shù)據(jù)格式可以根據(jù)需要設(shè)置,軟件默認(rèn)設(shè)置為遞增數(shù)據(jù)。圖5為自檢信號(hào)源數(shù)據(jù),該數(shù)據(jù)為00-FF遞增數(shù)據(jù)。將信號(hào)源數(shù)據(jù)下載到地面控制臺(tái)RAM中。

下載信號(hào)源成功后,將地面控制臺(tái)RAM中的數(shù)據(jù)讀入上位機(jī)來(lái)驗(yàn)證是否信號(hào)源正確。通過(guò)圖6所示的數(shù)據(jù)分析軟件可以詳細(xì)地檢驗(yàn)從RAM中讀回的數(shù)據(jù)是否準(zhǔn)確。

此數(shù)據(jù)波形驗(yàn)證了PCI Express傳輸卡能夠?qū)崟r(shí)無(wú)誤地傳輸數(shù)據(jù)。通過(guò)功能測(cè)試及數(shù)據(jù)分析可知,系統(tǒng)實(shí)現(xiàn)了任務(wù)中提出的功能要求,達(dá)到了技術(shù)指標(biāo)。

評(píng)論