基于VerilogHDL的CMOS圖像敏感器驅動電路設計

3 Verilog HDL驅動時序設計

經過以上分析可知,CMOS圖像敏感器采集時可以分為RESET過程和采集過程。時間上兩個過程是獨立的,如圖3。但在FPGA內部處理這兩部分的電路物理上是同時存在,因此必須將相應的信號通過置標志位的方法置為有效或無效。

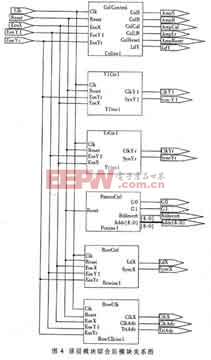

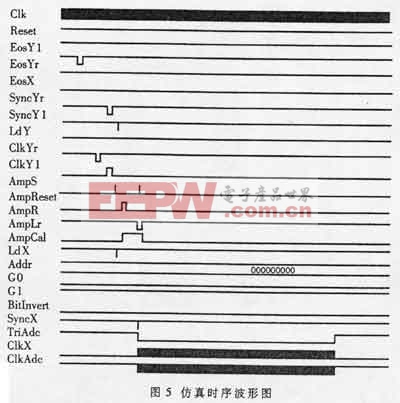

STAR250所需數字驅動信號共28個,其中SELECT信號在正常使用時,直接接PCB板的Vcc。因此需FPGA控制的驅動信號有27個。根據采集過程可以把信號劃分為列放大器信號,包括CAL、Reset、Lr、S、R、LdY。這6個信號在每一行的初始化部分都要用到,因此可以編寫到一個模塊(ColControl)中;模式信號(PaternCtrl)模塊用來設置CMOS敏感器的工作模式及初始地址,包括G0、G1、Bitlnvert和Addr[8:0]共12個信號。其中G0、G1用來設計輸出的放大倍數,BitInvert用于將輸出取反,Addr[8:0]則設置采集的起始地址;行讀出信號控制模塊(YlCtrl)產生行讀出地址的同步信號SyncYl及時鐘驅動信號ClkYl;行RESET信號控制模塊(YrCtrl)產生行RE-SET地址的同步信號SyncYr及時鐘驅動信號ClkYr;像素控制模塊(RowCtrl)產生行內像素初始地址的裝載信號LdX及同步信號SyncX;行內時鐘信號模塊(RowClk)產生列內像素的時鐘驅動CLKX、ADC驅動時鐘信號CLkAdc及輸出三態控制信號TriAdc。系統的輸入信號為主時鐘CLK、EosX行內像素結尾信號、EosYl幀內行結尾信號、EosYr幀內RESET行結尾信號、芯片的RESET信號。經過這樣劃分后的模塊化Verilog程序就比較易寫了。經過頂層模塊綜合生成的網表如圖4。布線仿真時序圖如圖5,其中時鐘信號過于密集變成黑色帶狀,同樣輸出時鐘CIkX及ClkAdc也是黑色帶狀。在時序上ClkX與ClkAdc是反相關系,在TriAdc保持低電平時輸出有效。所設計的驅動信號仿真波形與理論波形十分符合。這樣就完成了STAR250的時序驅動電路設計。

使用Verilog語言設計時序邏輯具有很高的效率。結合CMOS敏感器特性可以方便地開發出驅動時序電路。但必須對CMOS圖像敏感器的信號分析準確,正確分離那些獨立的信號和共用的信號,用時序邏輯設計驅動信號,用組合邏輯實現不同采集過程時間上的分離。布線延遲是必須考慮的,采用流水線技術可以預測延遲,保證信號的正確性。雖然文中并未給出像素ADC輸出的存儲電路,但實際上直接使用TriAdc信號作為SRAM的片選,ClaAdc的低電平作為寫信號,SRAM的地址在ClkAdc的上升沿增加、下降沿寫入。這樣就可以完成圖像數據的存儲。以上Verilog程序在FLEXl0kl0上布線實現。經示波器觀察邏輯正確,CMOS敏感器正常工作。

評論