基于NiosⅡ的學習型遙控器設計

2 硬件電路設計

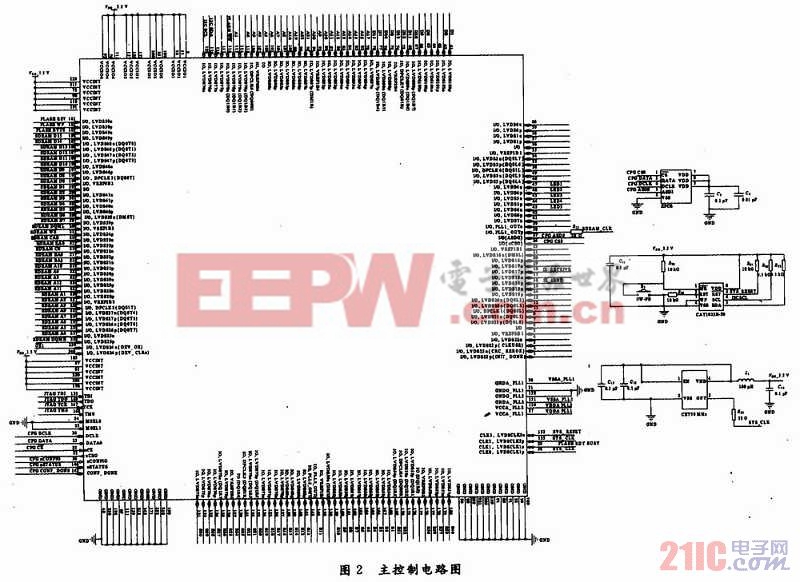

2. 1 主控制電路設計

主控制電路主要以Altera FPGA系列Cyclone EPlCl2Q240C8器件為載體,通過SoPC技術構建嵌入式軟核NiosⅡ處理器平臺,運用Verilog HDL硬件描述語言設計等精度測量載波頻率IP核、紅外信號解調IP核、紅外編碼脈寬測量IP核和紅外發送調制邏輯電路,以實現載波的精確測量,紅外信號解調、脈寬測量和調制功能。復位電路采用了專用看門狗芯片CATl025,以避免電路的死循環,同時也可以通過手動按下復位鍵,使系統重新啟動。時鐘是采用外部時鐘方式,其頻率為50 MHz。主控制電路圖如圖2所示。

2.2 外圍硬件電路設計

2.2.1 按鍵與指示電路

為了簡化軟件程序,結合FPGA多I/O口的優勢,本設計采用獨立按鍵方式,當按鍵按下時,FPGA對應的I/O口會檢測到低電平;按鍵彈起時,FPGA 對應的I/O口會檢測到高電平。對于指示電路,采用不同顏色的發光二極管來指示不同的狀態或控制不同的家用電器,當其中的一個指示燈閃爍時,表示正在學習對應的家電遙控器或者是發送對應的家電遙控信號。

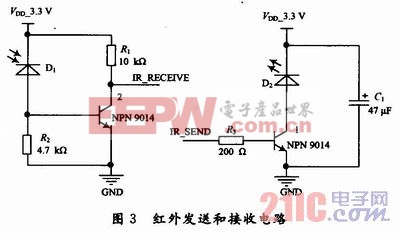

2.2.2 紅外接收和發送電路

紅外接收電路由紅外二極管、三極管9014及電阻組成。當未檢測到紅外信號時,紅外接收二極管電阻很大(近似于斷路),三極管9014處手截止狀態,此時 IR_RECEIVE端檢測到高電平;當檢測到紅外信號時,紅外接收二極管電阻較小,這時三極管9014發射極正偏,集電極反偏,三極管處于放大狀態。紅外信號通過共發射極電路放大后輸入到FPGA的I/O口18腳,交給Nios軟核進行處理。發送時,經過紅外發送調制邏輯電路調制后的紅外信號從FPGA I/O口16腳輸出,紅外信號通過三極管9014再次倒相放大后從集電極輸出,驅動紅外發射管輻射出紅外調制信號,從而實現紅外遙控信號的再生。紅外發送和接收電路如圖3所示。

2.2.3 存儲電路

存儲電路主要由AM29LV320DT(4 MB 16位并行總線)FLASH芯片和K4S641632H(64 MB 16位并行總線)SDRAM芯片組成。其中的SDRAM芯片起緩沖數據的作用,保存處理器及外部交換的數據信息,掉電或復位后數據丟失。FLASH閃速存儲器,用于SoPC系統的程序存放和需要掉電保存的數據存放,但是,FLASH的讀操作比SDRAM慢,寫速度更加緩慢(相對于SDRAM而言)。 NiosⅡ系統啟動后,在NiosⅡ的Boot程序把存放在FLA-SH中的程序復制到SDRAM后,再運行。

評論