PAD在接收機(jī)動態(tài)可重構(gòu)結(jié)構(gòu)中的應(yīng)用設(shè)計

PSoC器件集成了通過一個片上微控制器進(jìn)行控制的可配置模擬和數(shù)字電路,提供更強(qiáng)大的設(shè)計修改功能,并進(jìn)一步減少元件數(shù)量。PSoC器件包括最大32Kb的閃存、2Kb的SRAM、一個帶有32位累加器的8x8乘法器、電源和睡眠監(jiān)控電路,以及硬件I2C通信[2]。

所有的PSoC器件都是可動態(tài)重配置的,使得設(shè)計人員能夠隨意在運(yùn)行過程中改變內(nèi)部資源形式,使用較少的元件完成既定任務(wù)。易用的開發(fā)工具讓設(shè)計人員能夠選擇可配制程序庫元素來提供模擬功能(如放大器、ADC、DAC、濾波器和比較器),以及數(shù)字功能(如定時器、計數(shù)器、PWM、SPI和UART)。PSoC系列器件的模擬性能包括軌至軌輸入、可編程增益放大器和分辨率高達(dá)14位的ADC,以及超低的噪聲、輸入漏電流和電壓偏移。

單個PSoC器件可集成多達(dá)100個外圍部件,在提高系統(tǒng)質(zhì)量的同時,節(jié)省客戶的設(shè)計時間,縮減板級空間和功耗,并使系統(tǒng)成本降低。

接收機(jī)設(shè)計

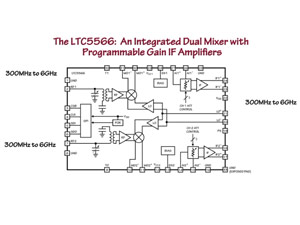

基于以上分析的結(jié)果,結(jié)合前端硬件電路,為實(shí)現(xiàn)一定的認(rèn)知無線電功能,特設(shè)計接收機(jī)結(jié)構(gòu)(見圖5)。

前端低噪聲放大器選用的是ADA4857-1,這是一個超低損耗、低功率、高速運(yùn)算放大器,在SOIC結(jié)構(gòu)下的3dB帶寬可以達(dá)到750MHz,其開環(huán)增益為57dB,基本滿足此接收機(jī)對前端低噪聲放大器的要求。在搭建電路時尤其要注意電源旁路、寄生電容和外圍器件的選擇對充分發(fā)揮放大器性能的影響[3]。

DDS(直接頻率合成器)選用的是1GSPS的AD9858,其使用先進(jìn)的DDS技術(shù)和一個內(nèi)置的高速、高性能D/A轉(zhuǎn)換器組成數(shù)字可編程、完全高頻率的合成器,可以產(chǎn)生一個高達(dá)400MHz的模擬輸出正弦波,完全滿足接收機(jī)對本振的要求。

混頻器、帶通濾波器、放大器和抗混疊濾波器都可以由Cypress的PSOC器件cy8c23x33來統(tǒng)一實(shí)現(xiàn)。PSOC模擬系統(tǒng)包括一個8位SAR ADC和4個可配置模塊,每個模擬模塊由一個運(yùn)算放大器電路組成,允許模擬復(fù)信號流的建立。同時,模擬外圍部件非常容易被定制從而滿足特殊應(yīng)用場合的需求。PSOC可以分別實(shí)現(xiàn)一個可編程帶通濾波器和一個低通濾波器以替代接收機(jī)前端需要的帶通濾波器和抗混疊濾波器,實(shí)現(xiàn)一個可選增益高達(dá)93dB的儀表放大器以替代中頻放大器,一個乘加累積器提供了一個快速8位乘法器以替代混頻器,以上可編程模擬器件均能基本滿足接收機(jī)前端性能要求。我們使用PSOC設(shè)計器進(jìn)行PSOC的工作配置,寫入使用PSOC的應(yīng)用程序并調(diào)試應(yīng)用。拿放大器來舉例,首先在設(shè)計器中找到這個模塊并新建一個電路,搭好外圍電路元件,按照建立時間、轉(zhuǎn)換速率和增益帶寬等幾個參數(shù)設(shè)定好初始值,產(chǎn)生應(yīng)用程序代碼,然后寫入主程序和子系統(tǒng)的任何子程序,如果所有程序正確,接著將產(chǎn)生一個HEX文件,最后由PSOC設(shè)計器中的調(diào)試器執(zhí)行,它下載HEX文件到在電路模擬器(ICE)中,至此一個可編程放大器設(shè)置完畢,可以投入使用。

可編程ADC本來可以由Cypress PSOC來實(shí)現(xiàn),但PSOC實(shí)現(xiàn)的ADC采樣速率最多只有375 Ksps,無法滿足認(rèn)知無線電接收機(jī)前端的帶寬要求,因此可以考慮使用SIDSA公司的FIPSOC器件,同時后端基帶數(shù)字處理任務(wù)也可交由FIPSOC中的8051核和FPGA兼而實(shí)現(xiàn)。利用運(yùn)行于WINDOW環(huán)境下的集成化開發(fā)工具,進(jìn)行ADC的設(shè)計和編程,結(jié)合上面介紹的一部分內(nèi)容,具體到ADC設(shè)計時還需要首先設(shè)置外部輸入/輸出引腳、內(nèi)部輸入/輸出引腳和內(nèi)部信號的初始化數(shù)值,然后再對mP控制寄存器和靜態(tài)RAM進(jìn)行配置,以達(dá)到所需要的性能要求。數(shù)字宏單元(DMC)是FPGA的可編程數(shù)字單元,它是基于查找表結(jié)構(gòu)的可編程單元,具有組合邏輯和時序邏輯資源,而組合部分和時序部分之間則由布線資源加以連接。利用動態(tài)重配置模式可對多個DMC單元進(jìn)行設(shè)置,可以改變硬件電路,進(jìn)而在一定程度上可對前端的可編程模擬器件進(jìn)行實(shí)時更新配置,這一技術(shù)目前正在探索研究中[4]。

以上只是各個模塊的分開設(shè)計,但是設(shè)計好整個接收機(jī)系統(tǒng),還需要對各個模塊之間的連線以及參考時鐘等許多方面給以足夠的重視。各個模塊都有屬于自己的輸入/輸出端口,為達(dá)到預(yù)定的系統(tǒng)性能要求,必須嚴(yán)格對照技術(shù)手冊和自己的預(yù)先布線安排接好各輸入/輸出端口。至于時鐘,避免采用時鐘抖動大的門電路是電路設(shè)計中需要嚴(yán)格遵守的準(zhǔn)則之一,在此基礎(chǔ)上才能最大限度地發(fā)揮器件的性能;除此,拿FIPSOC來說,除某些條件下,8051時鐘和其送至DMC的副本時鐘的相對相位會交換外,時鐘停止不影響時鐘同步;每次不同時鐘重新配置后,必須重新同步。

結(jié)語

目前,已經(jīng)在理論上證明了以上接收機(jī)結(jié)構(gòu)設(shè)計的可行性,下一步將逐步搭建出具體的硬件平臺并測試驗(yàn)證。除了可編程模擬器件外,新興的可進(jìn)化硬件(Evolvable HardWare,EHW)研究領(lǐng)域以硬件在線自適應(yīng)為目標(biāo),也將可編程模擬器件作為實(shí)現(xiàn)模擬電路自動設(shè)計和在線自適應(yīng)的重要評估手段和實(shí)現(xiàn)載體。可以預(yù)期,隨著模擬可編程技術(shù)的不斷進(jìn)步和器件品種的逐步豐富,可編程模擬器件將會成為實(shí)現(xiàn)模擬電路的首選器件和最佳選擇。

評論