PAD在接收機動態可重構結構中的應用設計

相位檢測器和低通濾波器一樣需要利用兩片TRAC器件來實現。而外部元件對于放大器和濾波器都是必不可少的,所以必須對滿足條件的元件進行合理取值。

可編程ADC的實現

認知無線電接收機對其前端采用的高性能模-數轉換器(ADC)及模擬器件的要求都較高,而FPGA在基帶數字信號處理方面又迫切需要動態可重配置。為了適應以上要求,可以首先考慮使用可編程模擬器件來實現ADC,以下是兩種具體實現方法。

FIPSOC混合信號片上系統

SIDSA公司的FIPSOC混合信號片上系統是快速開發模擬、數字集成應用的理想工具。FIPSOC芯片包括內嵌的增強型8051微處理器、現場可編程門陣列(FPGA)以及一組面向信號調理和數據采集應用的可靈活配置的模擬單元。與分離的模擬、數字FPGA方案相比,采用FIPSOC混合信號片上系統,可使產品設計周期縮短30~40%。

可編程的模擬、數字單元與8051的單片系統包括模擬單元、轉換單元、可編程數字單元、8051內核和該系列中的所有器件具有兼容的存儲器分布,其中轉換單元含有4路DAC(分辨率可配置為8至10位),采用逐次逼近算法,可利用這些DAC實現高達800KHz采樣率的ADC(見圖4)。

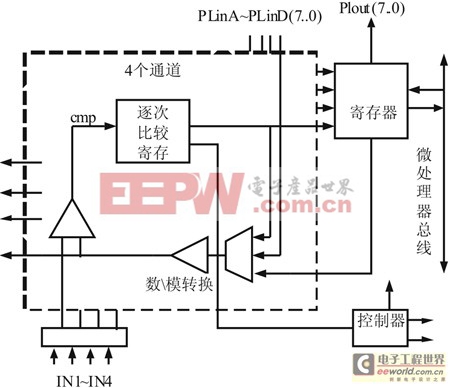

圖4 數據轉換模塊的框圖

數據轉換模塊包含4個8位的逐次比較寄存器(SAR),它可以和內部的DAC聯合工作,以獲得模/數轉換。

每一個通道有一個獨立的SAR,它接收逐次比較的結果,并驅動對應的DAC,每一個通道的轉換可以獨立進行。當轉換模塊編程為9或10位ADC轉換時,相應的SAR形成組:9位ADC時,SAR1和SAR2為一組,SAR3和SAR4為一組;10位ADC時,所有4個SAR形成一組。這時,成組的SAR各自工作1至2個周期,在轉換結束時,SAR將其內容寄存在輸入/輸出寄存器中,并使能中斷產生模塊。在連續轉換模式下,將啟動下一次轉換。在轉換過程中,可編程邏輯模塊可以獨立發布轉換命令,這將給本次以及下一次轉換帶來錯誤。在連續轉換模式下,這將導致致命錯誤,因為錯誤是可以傳遞的,并將得到不可預料的結果。

其控制部分是一個標準的8051微處理器。復合后,8051核首先對可編程元胞進行配置,配置完畢后可以當作一個通用的微處理器使用。為了更好的支持FIPSOC的動態可重構特性,已對其指令和功能單元做了一些改進。

CypressPSoC器件

Cypress半導體公司的PSoC混合信號架構將可編程的模擬與數字模塊同8位微控制器進行了完美集成,這種獨特的功能組合使設計人員能夠針對各種應用實現無與倫比的靈活性。最新CY8C23x33器件采用8位逐次逼近ADC,能實現高達375Ksps的采樣率。此外,該解決方案還具備可實現出色可配置性的26個GPIO,能夠快速適應不斷變化的特性要求。該器件采用5x5mm的QFN封裝,能夠最大限度地縮小板極空間。

評論