基于AD9516的寬帶高動態數字中頻系統采樣時鐘設計與應用

摘 要:數字中頻系統中高速ADC、DAC 對采樣時鐘有著很高的要求,對此設計了一種新的基于AD9516 的CDMA2000 數字中頻系統采樣時鐘合成方案。本文在提出該數字中頻系統硬件方案的基礎上,介紹了AD9516 芯片及其在本系統中的具體應用,給出了MCU 與AD9516 數據通信方式和芯片主要寄存器配置內容,且詳細分析了時鐘相位噪聲和時鐘抖動的測試方法。最終在對基于此時鐘方案制作出來的數字中頻系統PCB 板仔細調試之后,測試了時鐘相噪與抖動以及整個系統SNR ,整體指標達到設計要求。

本文引用地址:http://www.104case.com/article/162382.htm隨著3G 牌照的發放,在3G 網絡建設的初期,直放站是移動通信網絡優化的重要設備,而直放站核心部分數字中頻技術在現代通信系統中具良好的應用前景。但數字中頻系統主要部分ADC、DAC對采樣時鐘的要求很高,其在很大程度上決定了系統的整體性能。本文就該數字中頻方案所要求的采樣時鐘,設計了基于AD9516 的時鐘合成方案。與同類方案如某款芯片加外置VCO 比較,該方案在設計靈活性、芯片功能特性、電路簡單、成本低等方面均有很大的優勢。文中介紹了AD9516 芯片特性,著重說明了其在本方案中的具體應用,以及此處MCU 如何以FPGA 為橋梁與AD9516 芯片進行數據配置,還分析了時鐘相位噪聲與抖動對SNR 的影響,最后對制作出來的PCB 板進行了時鐘相噪與抖動以及系統SNR 的測試,結果證明該方案有很好的應用價值。

1 數字中頻系統整體硬件框圖介紹

本數字中頻系統射頻模擬輸入信號中心頻率為162 MHz ,10 MHz 帶寬的CDMA2000 信號,系統上下鏈路前后端均有衰減器對信號進行動態增益控制,該衰減器工作由FPGA 程序實行在線操作實現。硬件電路設計時系統要求選用高性能的ADC、FPGA、DAC 芯片,整個PCB 板由上下兩路射頻電路,時鐘部分,MCU 部分,以及電源組成,電路板上各個芯片的數據讀寫由ARM 單片機LPC2103 通過FPGA 控制。

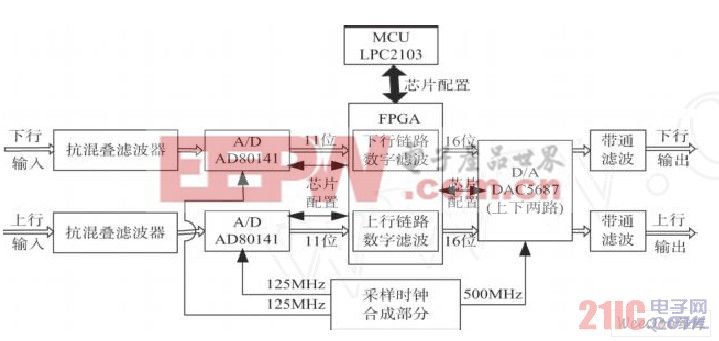

具體電路框圖及各部分芯片選用如圖1 所示:

圖1 整體硬件電路設計框圖

由于ADC、DAC 芯片都為高精度的數模轉換芯片,對時鐘的相噪和抖動有很高的要求,故必須選擇性能優異的時鐘合成芯片。根據所定的信號處理方案,時鐘合成單元需提供三路時鐘輸出作為上下兩路的ADC、DAC 的采樣時鐘。其中上下路ADC芯片為11 bit 、140 MSimple/ s 采樣速率的AD80141 各一片,需兩路125 MHz 時鐘;DAC 芯片為雙通道16 bit 、最高可達500 MSimple/ s 采樣速率的DAC5687 ,上下路共用一片,故只需一路500MHz 時鐘。

2 頻率合成單元設計

基于上述要求,綜合考慮提出一種新的基于AD9516 工作于內部VCO 模式的采樣時鐘合成方案,該方案無論從芯片功能、系統要求、設計的靈活性,還是同類方案成本方面都能很好的滿足項目要求。并且在整體中頻系統PCB 板布局布線時,會盡量考慮時鐘線的信號完整性,優化時鐘信號質量,測試結果證明所定方案完全符合要求。

2.1 AD9516 芯片簡介

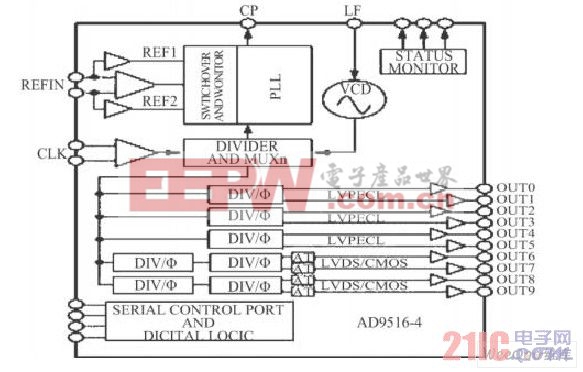

頻率合成單元采用AD 公司的AD9516 芯片,它是一款集低相位噪聲時鐘發生和低抖動14通道時鐘分配功能于一體的時鐘合成器,其結構圖如圖2 所示:

圖2 AD9516 結構圖

評論