一種高速EM CCD 圖像傳感器CCD97時(shí)序驅(qū)動(dòng)電路的設(shè)計(jì)方法

2. 2. 1 I Φ, S Φ, RΦ 驅(qū)動(dòng)設(shè)計(jì):

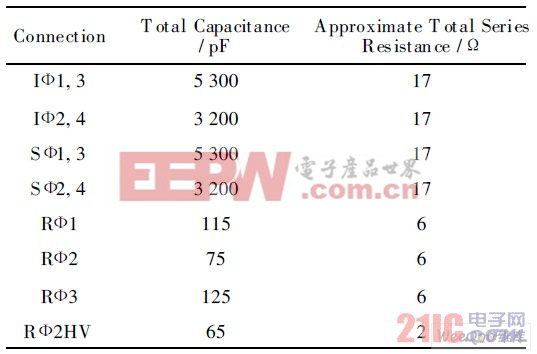

在設(shè)計(jì)I Φ, SΦ 以及RΦ驅(qū)動(dòng)電路時(shí), 統(tǒng)一采用Elantec 半導(dǎo)體公司的EL7457。它是高速四通道CMOS 驅(qū)動(dòng)器, 能工作在40 MHz, 并提供2 A 的峰值驅(qū)動(dòng)能力, 以及超低的等效阻抗( 3Ω ) , 它具有3 態(tài)輸出, 并通過(guò)OE 控制, 這對(duì)于CCD 的驅(qū)動(dòng)來(lái)說(shuō), 容易實(shí)現(xiàn)靈活的電源管理。為了簡(jiǎn)化設(shè)計(jì), 固定RΦ2HV 的電壓幅值為典型值。在組成IΦ和S Φ 的驅(qū)動(dòng)電路時(shí)必須考慮CCD97 驅(qū)動(dòng)端的等效電容和電阻, 如表2 所示。

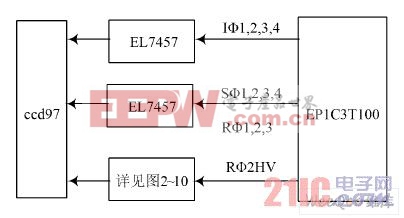

圖5 CCD97 驅(qū)動(dòng)電路結(jié)構(gòu)原理框圖

表2 CCD97 驅(qū)動(dòng)端等效電容及電阻

電路的時(shí)間常數(shù):

又因?yàn)樯仙龝r(shí)間與時(shí)間常數(shù)的關(guān)系為:

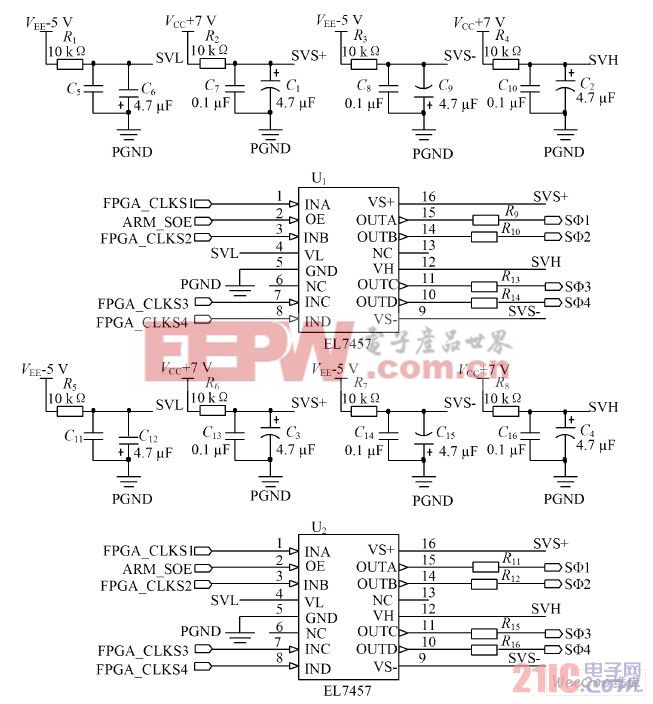

為了滿足最佳上升時(shí)間( 200 ns) 的要求, 必須在EL7457 驅(qū)動(dòng)輸出端串上一個(gè)小電阻, 原理如圖6 所示。

圖6 中, FPGA _ CLKI1, FPGA _ CLKI2, FPGA _CLKI3, FPGA _ CLKI4 為FPGA 產(chǎn)生的T T L 時(shí)序。

ARM_IOE 為ARM 核產(chǎn)生的門控信號(hào), 用來(lái)控制驅(qū)動(dòng)脈沖I Φ1, 2, 3, 4 的開(kāi)關(guān)。由于理論與實(shí)際計(jì)算的誤差, 輸出串接電阻R9 , R10 , R 13 , R14 將通過(guò)硬件調(diào)試過(guò)程確定, 以產(chǎn)生驅(qū)動(dòng)CC97 工作的最佳波形。同理, FPGA_ CLKS1, FPGA _ CLKS2, FPGA _ CLKS3, FPGA _CLKS4 為FPGA 產(chǎn)生的TT L 時(shí)序。A RM _SOE 為ARM 產(chǎn)生的門控信號(hào), 輸出串接電阻待定。

圖6 IΦ 1, 2, 3, 4; SΦ 1, 2, 3, 4 驅(qū)動(dòng)產(chǎn)生

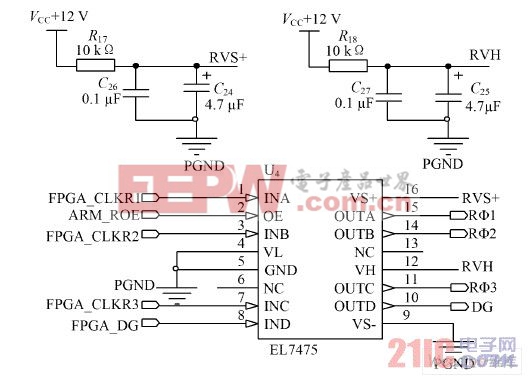

在RΦ1, 2, 3 產(chǎn)生電路中, 因?yàn)槠潆妷簲[幅要求為0~ 12 V, 故給它加以12 V 的電源( 見(jiàn)圖7) 。

圖7 RΦ1, 2, 3 驅(qū)動(dòng)產(chǎn)生電路

它的驅(qū)動(dòng)頻率為11 MHz, 輸出的上升時(shí)間不需要串接電阻調(diào)節(jié), 可達(dá)10 ns。同理, FPGA_CLKR1, FPΦGA_CLKR2, FPGA_CLKR3 為FPGA 產(chǎn)生的10 MHz的驅(qū)動(dòng)時(shí)序, ARM _ROE 為ARM 產(chǎn)生的門控信號(hào)。

DIY機(jī)械鍵盤相關(guān)社區(qū):機(jī)械鍵盤DIY

評(píng)論